### D R ∧ P E R<sup>™</sup>

# **The Dover Architecture**

Hardware Enforcement of Software-Defined Security Policies

Team: Greg Sullivan (Draper) (presenting), André DeHon (UPenn), Eli Boling, Marco Ciaffi, Steve Milburn, Nirmal Nepal, Jothy Rosenberg, Andrew Sutherland (all Draper)

Date: November 28, 2016

New England Security Day Fall 2016 At Worcester Polytechnic Institute, Worcester, MA

The Charles Stark Draper Laboratory, Inc. 555 Technology Square, Cambridge Mass. 02139-3563 CAGE Code: 51993

#### INHERENTLY SECURE PROCESSING

- 1. Brief history lesson and motivation

- 2. Brief overview of Dover hardware architecture.

- 3. Introduction to policies, as enforced on Dover

- 4. Motivation for discussion: more uses for policies.

### **Dover pre-history**

### 2010-2015 – DARPA CRASH program – Clean Slate Security

- CRASH SAFE project (prime = BAE Systems) included U. Penn (DeHon, Pierce, Smith), Harvard (Morrisett), Northeastern (Wand, Shivers)

- Clean slate hardware, ISA, programming languages, runtime

- Tagged architecture every word has metadata, every instruction vetted by software-defined policies

- Formal verification of security policies, with a focus on information flow control (IFC)

- ASPLOS 2015: Can we add tags and "PUMP" (Programmable Unit for Metadata Policies) to conventional RISC processor?

- papers at <u>http://www.crash-safe.org/</u>

- Lots of earlier history: TIARA project (Knight, Shrobe, DeHon), other tagged architectures (Intel 432, IBM System 38, Lisp Machines, etc.), information flow PLs and Oses.

#### DRAPER<sup>™</sup>

### **Motivation – Software Security Problem**

Virtually impossible to write C/C++ code without vulnerabilities

- Static analysis, formal verification: gets you part way.

- Testing: gets you part way.

- Software-based runtime security monitors: hopeless

- Signature-based: useless, by definition, for 0-days

- IRMs, stack canaries, ASLR, etc. subvertible

- "Eternal war on memory"

You can't fix buggy software with more (buggy) software.

Need hardware as root of trust.

$\mathsf{D} \mathsf{R} \wedge \mathsf{P} \mathsf{E} \mathsf{R}^{\mathsf{m}}$

#### **DR** ∧ PE R<sup>™</sup>

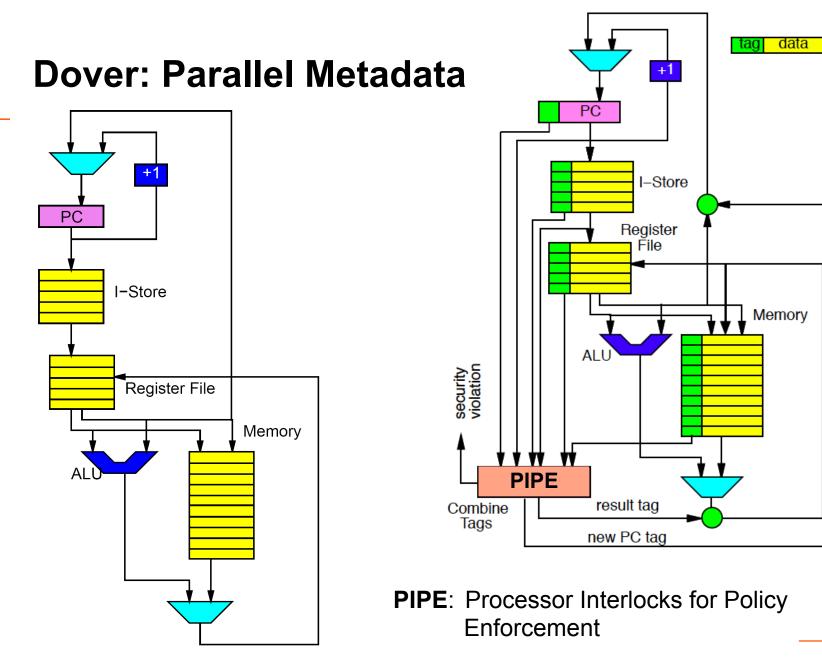

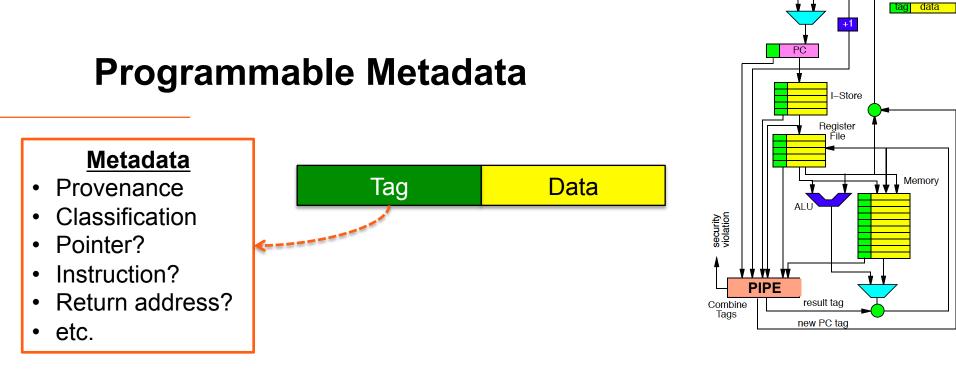

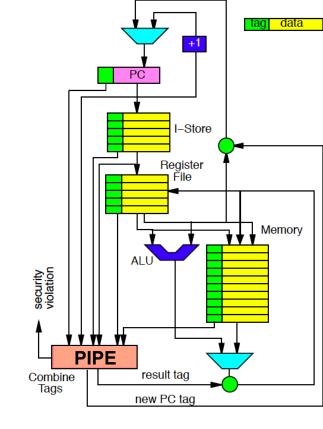

- Give each word a programmable tag

- Indivisible from word

- Uninterpreted by hardware

- Software can use as pointer to data structure

- Tags checked and updated on every operation

- Common case in parallel by PIPE "rule" cache

#### $\mathbf{D} \mathbf{R} \wedge \mathbf{P} \mathbf{E} \mathbf{R}^{\mathsf{T}}$

### **Abstract Function**

- Every word may have arbitrary metadata

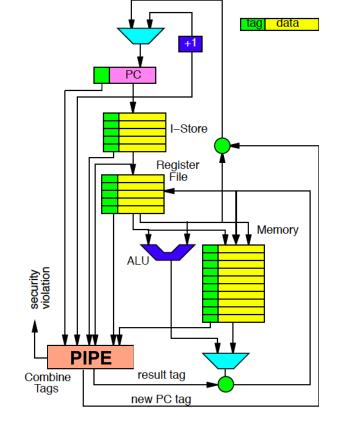

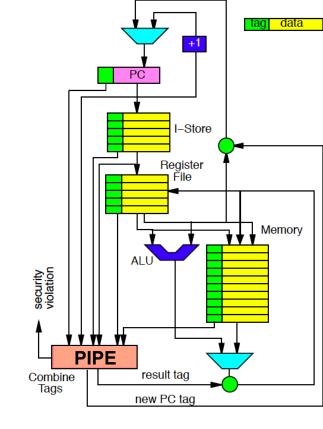

- PIPE is a function from:

- Opcode,  $PC_{tag}$ ,  $Instr_{tag}$ ,  $RS1_{tag}$ ,  $RS2_{tag}$ ,  $MR_{tag}$

- To:

- Allowed?

- PC<sub>tag</sub>

- Result<sub>tag</sub> (RD, memory result)

Policies

# What operations are allowed and how metadata is updated

Examples:

- Memory Safety

- Control Flow Integrity

- Taint tracking / Information Flow Control

- Access Control (fine-grained)

- Mandatory Access Control

- Types (including application-defined)

- Fine-grained instruction permission

####

### **Composite Policies**

- Limiting if only support one policy at a time

- Use pointer tag to point to tuple of µpolicies

- No hardware limit on number of µpolicies supported

- Support 0-1-∞ design principle

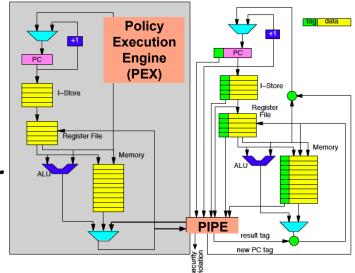

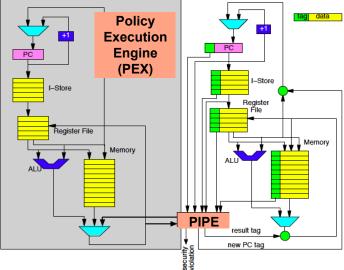

### **Separation**

Policy Execution Engine (PEX) Coprocessor

- Data and Metadata do not mix

- Metadata not addressable

- Datapaths do not cross

- No instructions read or write metadata

- No set-tag, no read-tag

- All metadata transforms through PIPE

#### $\mathbf{D} \mathbf{R} \wedge \mathbf{P} \mathbf{E} \mathbf{R}^{\mathsf{m}}$

### **Project Status**

#### Hardware

- Building around RISC-V (open source ISA specification)

- see <u>https://riscv.org/</u>

- Implemented on FPGA.

- 1<sup>st</sup> version used Bluespec/Verilog. Current version uses just Verilog

- Aiming for ASIC tape out June 2017.

- Both Application Processor (AP) and PEX based on 32b Rocket open source RISC-V design

### **Project Status, continued**

#### Software

- simple "Dover Kernel" useful for experimenting with policies.

- Most complicated bits: booting initializing PEX and AP; loading ELF images and applying tags to instruction words.

- modified GCC RISC-V cross-compiler to generate metadata used by loader for CFI, stack safety policies.

- modified RISC-V software simulator ("spike") to mimic AP+PEX design

- Domain Specific Language for writing policies.

- generates C

#### $\mathbf{D} \mathbf{R} \wedge \mathbf{P} \mathbf{E} \mathbf{R}^{\mathsf{m}}$

# **Fun With Policies**

### Memory Safety *µ*-Policy

Goal: enforce spatial and temporal safety

- **Method**: give each pointer a unique "color" •

- color memory slots with this color on allocation

- recolor on free

- **Policy**: •

$$(LOAD, -, -, R1, -, MR) \Rightarrow (MR = R1, -, -$$

Require that tag (color) on pointer (R1) equals tag on pointed-to word (MR)

similar for STORE

Reminder: (opcode, PC, INST, OP1, OP2, MR) → (allow?, PC, Result)

####

= 0xbad; //FAIL

y[3]

x[2]

### Control Flow Integrity µ-Policy

Goal: limit control transfers to those specified by program

Copy tag from call instruction to PC tag **Policy**: •  $(CALL, none, t1, R1, -, -) \Rightarrow (true, t1, -)$  $(CALL, t1, t2, -, -, -) \implies (t1 \text{ in } t2, \text{none}, -)$ foo { If not a call instruction, and PC is tagged (e.g. t1), t1: bar() : control flow transfer check that tag on PC (t1) is in the list of "legal t4: caller tags" (t2) on current instruction (which must t2: bar  $\{$ be the target of a call). Also, untag PC back to none. t3: return; has CFI metadata  $t2 \rightarrow \{t1, t42, ...\}$ Generalize for return

Reminder: (opcode, PC, INST, OP1, OP2, MR) ⇒ (allow?, PC, Result)

DRAPER<sup>™</sup>

### **Taint Tracking** *µ***-Policy**

- **Goal**: track influences of values

- prevent untrusted values influencing critical decision

- limit flow of sensitive data

- Policy:

```

(ADDL, PC, INST, OP1, OP2, -) →

(true, PC, union(PC, INST, OP1, OP2))

Tag (taint) on result is union of taints on operands.

```

Reminder: (opcode, PC, INST, OP1, OP2, MR) ⇒ (allow?, PC, Result)

# **Questions for Discussion**

### **Discussion Topics**

#### How to use metadata to implement / enforce:

- Least privilege compartmentalization

- Information flow, à la MLS (multi-level security) or more general

- Linear / Affine types (e.g. use at most once, cannot copy, etc.)

- Canonical example: A return address should not be copied.

- Stack safety (vs. heap memory safety using colors)

- Intra-structure safety (e.g. two arrays w/in same struct prevent overflow from one into another).

- Fully abstract compilation (being pursued by Cătălin Hriţcu et al. under ERC SECOMP project)

- call untrusted reverse restrict access to contents of list elements.

- call untrusted sort restrict access to calls to <= or compare on elements.

####

Some pointers:

- CRASH SAFE papers: <u>http://www.crash-safe.org/papers.html</u>

- Draper Inherently Secure Processor project: <u>http://www.draper.com/solution/inherently-secure-processor</u>

- RISC-V: <u>https://riscv.org/</u>

This Document Does Not Contain Controlled Technology or Technical Data

**Draper Proprietary**