### CORRECTNESS IN OPERATING SYSTEMS

Hugh Conrad Lauer

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at Carnegie-Mellon University, Pittsburgh, Pennsylvania

September, 1972

This work was supported by the Advanced Research Projects Agency of the Office of the Secretary of Defense (F44620-70-C-0107) and is monitored by the Air Force Office of Scientific Research. This document has been approved for public release and sale; its distribution is unlimited.

This work was supported by the Advanced Research Projects Agency of the Office of the Secretary of Defense (F44620-70-C-0107) and is monitored by the Air Force Office of Scientific Research. This document has been approved for public release and sale; its distribution is unlimited.

### Acknowledgements

- I am deeply indebted to Professor Alan Perlis, the source of a continuum of interesting ideas and problems, for his wisdom and inspiration of this work;

- to Professors William Wulf and A.N.Habermann, my principal advisers, for their guidance through this research, particularly in its formative stages;

- to Professors B. Randell, James J. Horning, and William Lynch, who through their stimulating discussions and subtle browbeating taught me to keep the faith and to keep my feet on the ground;

- to Mrs. Dorothy Josephson, for her wizardry with the typewriter in producing this document:

- and most of all, to my wife Ruth, who patiently typed countless notes and rough drafts, lest I not be able to read my own work, who listened attentively to and believed my wildest ideas, lest I lose my own confidence, who spent many a lonely evening silently watching me stare at those horrible formulas, never once losing hope that we could beat them into submission but for her, I would have given up long ago.

| ÷+. |  |  | )   |

|-----|--|--|-----|

|     |  |  | 1   |

|     |  |  | Į.  |

|     |  |  | 1   |

|     |  |  | į   |

|     |  |  |     |

|     |  |  |     |

|     |  |  | 1   |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  | ŧ   |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  | γ { |

|     |  |  | !   |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  | 1   |

|     |  |  | į   |

|     |  |  |     |

|     |  |  | j   |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  | 1   |

|     |  |  | 1   |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  |     |

|     |  |  | k . |

|     |  |  |     |

|     |  |  | k . |

|     |  |  | k . |

|     |  |  | k . |

|     |  |  | k . |

#### ABSTRACT

In a method of program verification introduced by Floyd, assertions are attached to a flowchart description of a program, and correctness is established by showing their consistency with respect to that flowchart. In this thesis, the method has been extended to apply to concurrently executing programs such as those which occur in operating systems. This has required a careful definition of process and an effective representation of the interactions among processes. For this purpose, a flowchart-like representation was chosen to characterize all possible computations resulting from the asynchronous execution of two programs. Floyd's results were then applied to this representation to transform a problem of verifying a set of programs into a problem of proving a theorem of logic. Simplifications suggested by the structure of the programs are applied to reduce the level of difficulty. Transformations suggested by the interactions of the programs are applied to facilitate the effective characterization of properties of interest.

The verification methods are applied to several small examples of systems of cooperating processes. They illustrate that interesting properties can be proved about such systems but that there are still many unsolved problems. In particular, a precise formulation of the concept of an abstraction of a process is required. The thesis concludes with a presentation of a possible formulation of such a concept and a brief exploration of its properties.

|   |   | . )        |

|---|---|------------|

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

| • |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   | ٠,         |

|   |   |            |

|   |   |            |

|   |   | Ł.         |

|   |   |            |

|   |   |            |

|   | · |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   | • |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   | <i>'</i> ' |

|   |   |            |

|   |   |            |

|   |   | ŧ          |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   |            |

|   |   | 1          |

|   |   |            |

|   |   |            |

|   |   | 1          |

|   |   | 1          |

# TABLE OF CONTENTS

|            | Page                                            |

|------------|-------------------------------------------------|

|            | Introduction                                    |

| I.         | Information, Processes, and Operating Systems 9 |

| II.        | Transition Graphs                               |

| II.        | Proving Correctness of Cooperating Processes 44 |

| IV.        | Some Other Forms of Correctness                 |

| <b>V</b> • | Abstractions of Processes                       |

|            | Comments and Conclusions                        |

|            | Bibliography                                    |

|  |   | v  |

|--|---|----|

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   | Í  |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  | · |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   | c. |

|  |   | `  |

|  |   |    |

|  |   |    |

|  |   | ,  |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

|  |   |    |

#### INTRODUCTION

This thesis considers ways of establishing the correctness of properties of cooperating processes. It extends the work of Floyd [1967], Manna [1968], King [1969], and others to include programs which execute "concurrently". It is complementary to the theoretical work of Dijkstra [1965a], Habermann [1969], Holt [1971], and others in considering the accuracy of programs which occur in operating systems. Hopefully, it will provide some insight and will lead to techniques to help solve the problem of constructing large, complex operating systems which work properly.

The difficulty of programming and debugging systems in which several coordinated activities proceed concurrently has been documented by Dijkstra [1965a], Van Horn [1966], Wirth [1969], and others, and it has become painfully apparent to systems programmers in recent years. Such systems are generally not deterministic, in the sense that from a given starting point, one could reach any of a number of different states, depending upon the relative speeds of the component activities. Errors are often difficult to trace because they are caused by events of which all record has vanished, and they are more difficult to reproduce because they depend on rare (or unknown) combinations of circumstances which cannot be readily duplicated.

There are two useful, complementary approaches to the problem. The synthetic approach concentrates on developing programming techniques which avoid the pitfalls of parallel activities and which ease the burden created by problems of scale in system design. The analytic approach

concentrates on examining systems to identify the potential trouble spots and/or to show that they do not exist. The latter category includes various techniques, one class of which involves attempting to verify programs with respect to <u>assertions</u> describing the properties in question. In this thesis, we will concentrate on proving the correctness of concurrently executing programs by showing the consistency of such assertions. With the exception of some work reported by Ashcroft and Manna [1971], none of the existing assertion-oriented techniques applies directly to systems of concurrent processes. But we shall see that by adopting a suitable representation, these methods can be extended to apply.

Whether or not it is practical and/or useful to prove a program correct, particularly in formal terms, is the subject of many heated debates. Furthermore, it is unlikely that anyone will, in the near future, be able to prove that a large operating system is correct - simply because it is too difficult. Even so, there are many reasons why we should develop the formal apparatus for doing so. First, proving correctness is an interesting mathematical problem in its own right. It is nice to know under what circumstances it can be done and how to do it. It is also nice to know what constraints the peculiarities of concurrent execution present to the problem.

Another, perhaps more compelling, reason for developing verification techniques is that they may lead to useful synthetic techniques for building systems which are a priori correct and which display a better organization than our present ones. This is already happening with sequential programs. Naur [1969] and Hoare [1971] have combined

a constructive approach to program design with their methods for formally proving correctness. Both have demonstrated the development of simple sequential programs using these techniques. Similarly, Henderson and Snowden [1971] have shown that program verification methods are an important conceptual tool to use with the structured programming techniques of Dijkstra [1970] - not so much for proving a program correct as for helping the programmer to maintain suitable relationships between its parts.

Formal verification methods are also useful in analyzing abstract models of various system functions. For example, Ladner [1970] has used the results of Floyd [1967] to establish the theoretical basis of his analysis techniques for communication algorithms, even though those techniques themselves bear little relation to formal logic and theorem proving. We might reasonably expect that an understanding of how to verify the programs of an operating system would be useful in constructing analytic methods to apply to such systems. Similarly, we can hope that understanding the formal techniques would lead to better understanding of the systems themselves and of the laws which govern their structure and behavior.

Finally, we will show in this thesis that our verification techniques can be applied to some very small programs. We may, in the course of future research on system structure, discover ways to reduce the dependence of system reliability on correct code. If that is done, then it will be sufficient to verify only small, critical programs to establish some confidence in a system with a suitable structure. I.e., while it would be

too difficult to consider verifying a whole system, we may obtain useful information by verifying small pieces of it.

The kinds of programs which occcur in operating systems are often quite different from those we write for many other applications. The programs, which comprise the central "monitor" and the various "system processes", usually share some of their variables with others, and the values of these variables are liable to be changed by any of the programs at almost any time. Thus they are non-deterministic - that is, their execution is not predetermined by any observable state. These programs rarely halt and are usually designed not to. Instead, they loop, continually looking for more work to do and regularly transferring important status information from one iteration to another. Thus, it is pointless to try to prove them correct with respect to the traditional criteria that they halt and that the output be a given function of the input. We must develop more appropriate criteria.

Programs in operating systems also suffer from errors which are not considered by existing verification methods. For example, they may become "blocked" and prevented from further execution. A whole system becoming blocked represents a sort of catastrophic error which we would prefer not to happen. Another example involves the problem of protecting information. Design errors which allow faulty or malicious programs to access variables which they should not must be discovered and eliminated. We need appropriate criteria of correctness to cover this kind of problem, as well.

We do not claim to have developed a complete set of criteria and formal verification methods appropriate for operating systems. But the

results of this thesis are a beginning. We will define correctness in terms of predicates which assert some relationship among the values of the variables of the programs. Because we are considering programs which execute concurrently and which exchange information, we must pay careful attention to their representation and the representation of their interactions. To this end, we will develop a flow-chart-like notation which will become the basis for our verification techniques. Then, as an extension of Floyd's Induction Theorem [1967a], we will show that a problem of verifying a system of cooperating processes can be reduced to proving a theorem of the first-order logic in a particular interpretation. Methods for proving several other forms of correctness are derived from this by suitable transformations to the problems or the programs.

In the course of this research, it became apparent that apart from the tedium of proving theorems of logic, one of the greatest difficulties in verifying a system of programs is finding an appropriate statement of correctness which can be proved. In the case of several simple systems, the "obvious" statements about the programs do not contain enough information to allow a proof and the author was not able to find less obvious, but provable, statements. This demanded new techniques which allow us to infer the correctness of a system from some additional information. To do this, a second system is constructed from the first by adding redundant information or identifying certain states and changing the representation slightly so that a statement of correctness is more convenient. Then we can prove that the correctness of the second system implies that of the first.

Finally, we will see that the methods developed in the thesis are not restricted to machine level programs but can be applied to more abstract representations, as well. A verification of a system can then be factored into two parts: a verification of the abstract representation and a demonstration that the representation itself accurately reflects the system. This may be easier than considering the system as a whole, and it is a natural consequence of systems designed in "levels of abstraction", such as the THE System (Dijkstra [1968b]).

It is worth pointing out that the author's interest in this research has been directed toward the structure and correctness of computer operating systems. As such, the theorems and examples are biased in that direction. But neither the results of this thesis nor the assumptions from which they are derived are peculiar to operating systems problems and, in fact, can be extended to any system of cooperating processes at any level of abstraction. The reader is invited to generalize whenever and wherever he wishes.

#### Outline of the Thesis

The following material is divided into five chapters. In the first chapter we will develop a formal model of computation, inspired by the informal point of view of Dijkstra [1965a] and the semi-formal model of Horning and Randell [1969]. This model is oriented toward the problem of representing combinations of processes, and it forms the basis of our verification techniques. It is also useful in considering the more general problem of forming "levels of abstraction" or abstract representations of systems of processes, as will be seen in Chapter V.

In Chapter II we adapt Manna's graphical representation of processes to account for concurrent computation. These graphs, which we designate as transition graphs, are similar to flowcharts, but with the roles of the arcs and nodes reversed. That is, in a conventional flowchart the nodes (or boxes) represent actions and the arcs between nodes correspond to the states between actions, whereas in the transition graph, the arcs represent the actions and the nodes correspond to the states between actions. Several simple theorems will be proved to show that a transition graph formed from those of a system of concurrent processes represents the combined effect of their simultaneous operation.

In Chapter III we present a definition of correctness and extend Floyd's Induction Theorem to apply to cooperating processes. This is done by generating a formula of logic from the transition graph representing the system of processes. Then the system can be proved to be correct if those predicates satisfy the formula - i.e., if they cause it to be true, when substituted for the symbols of the formula in an orderly way. Finally in this chapter we will present some techniques for reducing the complexity of a verification based on the structure of the system.

In Chapter IV we consider three additional ways of stating and proving correctness. In the first, the transition graph representing a process or system is extended with redundant information to allow a convenient way of making assertions about the states of the system which cannot be made only in terms of its variables. These simplify proofs of correctness considerably. In the second, we consider ways of stating and proving that something does <u>not</u> happen in a system - i.e., that certain combinations of states never occur. This method is useful provided that

those combinations can be identified. If not, the third method may help. It allows us to prove that something does not happen (for example, a deadlock) by proving instead that something else always happens (for example, the processes always reach a home state in finite time). The last two techniques are based on the termination results of Manna [1968] for non-deterministic processes.

In the final chapter we investigate the question of what circumstances permit the correctness of a system to be established from an "abstraction" rather than from the system itself. We will consider the conditions under which it is possible to consider the cooperation of abstract processes without reference to their underlying implementation. In particular, the methods of previous chapters suggest, in principle, a method of verifying that an alleged abstraction of a process correctly represents that process.

#### CHAPTER I

# INFORMATION, PROCESSES, AND OPERATING SYSTEMS

To prove the correctness of a set of cooperating processes, we must know precisely what is meant by the term process and by the idea of cooperation or communication among several of them. Horning and Randell [1969] have given a survey of some definitions of these terms and have extracted the essential elements into a model of the computation done by cooperating processes. In this chapter we extend that model to overcome their difficulty in characterizing "asynchronous" cooperation.

This is done by incorporating Dijkstra's important, abstract assumption that all actions in a system are timeless and no two actions occur at exactly the same instant. Thus in our model, there is never any conflict among processors about assigning a value to a variable. This abstraction bears no more relation to reality in computing than does the postulation of frictionless surfaces in physics. But it is useful for solving a large class of problems, including those of this thesis. It is, of course, possible to simulate such a world, and many hardware and software systems do to some extent. As a result we can factor a proof of correctness into parts: (1) a verification of the abstract system (using the assumption) and (2) a proof that the real system being verified correctly simulates this timeless environment. In this thesis we will concentrate on the first part, but we will comment on the second part in Chapter V.

With the current proliferation of models of computing, one may

question the value of introducing yet another. Our model will be justified if it persuades the reader that our results on proving correctness are relevant to programs which occur in operating systems. It may also be useful in solving problems beyond or orthogonal to the scope of this thesis; if that happens, it will be additional justification. On the other hand, when the results obtained with it can be understood more simply without it, then it will be time to relegate it to the role of an historical curiosity.

We will begin with the primitive, intuitive concepts of information and processor which form the basis of our programming experience. From this, we will define the union and intersection of information sets and the product of two processors. The terms computation, process, and combination of processes are based on these definitions. An essential consequence of the definition is that a process may be formed from the union of two information sets and the product of two processors, and this process represents the behavior of two processes interacting with each other. Thus all of the results about processes apply to combinations of them as well. Finally, in this chapter, we will characterize operating systems from the point of view of the model and of establishing the correctness of their components.

### Information Sets

The basic stuff in computing is <u>information</u>. It occurs in sets of <u>information elements</u>, and each element is an object which has a distinct identity or name and which can assume any of a domain of <u>values</u> or <u>states</u> (these last two terms are synonymous for our purposes). Examples of

information include a bit, which can have either of two values, a 32-bit word, which can have any of  $2^{32}$  distinct values, or an Algol integer variable, which (in the most abstract sense) can have any of the integers as value. In the discussions which follow, we will not be concerned with any internal structure of information elements. Instead, they will be regarded as primitive, indivisible objects defined only by our programming intuition.

An <u>information set</u> is a named set of information elements, and its value or state is the set of values of its elements. Examples of information sets include the set of variables of a program, a collection of files in an operating system, and programs or systems of programs themselves. Another, more abstract, example is the potentially infinite set of incarnations of the variables of a recursive Algol program. While the structure of an information set is of paramount importance in program design, it will not be of concern to this discussion. We are only interested in the composition of information sets - i.e., which elements are contained in it - and its value, regarded as a whole.

In practice, we deal only with finite sets of information elements, each of which can have only a finite number of values. However, it is often convenient to imagine infinite information sets for purposes of simplifying analysis. For example, we often assume that we can do arithmetic on the set of all integers, even though our computers use one or another system of finite arithmetic (see Hoare [1969]). Our model will accept axioms for either system and is, in general, not restricted by any finiteness assumptions. We will, however, take advantage of finiteness where it naturally occurs.

In order to consider communication and cooperation among processes, we will need to form combinations of information sets. The following notation will be useful:

Let the upper case letter X, Y, Z, X', Y', etc., denote information sets, and let corresponding lower case letters (possibly subscripted) denote their values. I.e.,

$$x,x_1,x_2...$$

and

will denote values of the information sets X and Y', respectively. Because information sets are sets of information elements, it makes sense to consider the set-theoretic operations  $\cup$ ,  $\cap$ , and  $\setminus$  (i.e., union, intersection, and set difference) on them. Then, if X and Y are two information sets, then we will use the notation  $x \cup y$ ,  $x \cap y$ , and  $x \setminus y$  to denote the values of  $X \cup Y$ ,  $X \cap Y$ , and  $X \setminus Y$ , respectively, where x is the value of X and y is the value of Y. That is, the symbols " $\cup$ ", " $\cap$ ", and " $\setminus$ " do not define operations on the values of information sets. Instead, they are a convenient way of representing the values of the corresponding combinations of two information sets in terms of the values of their components. Finally, if the information set X is a subset of Y, we will use notation  $y \mid X$  (read "y restricted to X") to denote the value of X in terms of the value of Y.

#### **Processors**

Information is useful in computing because its value can be changed

in well-defined, mechanical ways. The act of computing is the act of repeatedly transforming the value of an information set with the aim of producing some value with a specific meaning in the context of the problem being solved. The instruments of computing are processors - i.e., real or conceptual devices which implement sets of rules specifying how the values of information sets are to be changed or transformed. A processor is generally designed or defined to manipulate a particular information set (class of information sets), which we will call its operand. Each of the possible changes in value that the processor can make upon an operand is called an operation.

A processor may be a hardware automation, a program, or some conceptual entity. For example, the Central Processing Unit of a computer system is a processor which operates on an information set consisting of core memory, accumulators, and whatever other registers it may have. The rules which it implements are those described informally in its programming manual. Alternatively, a processor could be a program written in some language to specify how variable data is to be transformed in value. The operand in this case is the set of variables of the program. Interpreters of languages such as LISP fall into this category: in effect, they create imaginary processors to implement the rules of transforming information as defined by the semantics of the language. The art of programming is, then, the act of defining one or more processors and information sets, usually in terms of other processors and information sets.

This idea of processor is, of course, intuitively obvious and fundamental to competent programmers. It will form the basis for

precise definitions of computation and process and it will be convenient for describing the communication among processes. Before we proceed with these definitions, it is useful to introduce some additional notation.

Suppose Q is a processor and the information set Y is its operand. If Q defines an operation on the value of Y from  $y_0$  to  $y_1$ , then we say

$$y_0 \xrightarrow{Q} y_1$$

i.e., that  $y_1$  is a <u>successor</u> of  $y_0$  under Q. It may be the case that some values  $y_0$  of Y, have no successor values. These are called <u>blocking states</u> of Q, and Q is said to be <u>blocked</u> when Y has one of these as its value.

### Example:

A processor Q is defined such that one of its operations is the <u>P-operation</u> (Dijkstra [1965]) on a particular variable of type <u>semaphore</u>. The P-operation reduces the value of the semaphore by one <u>provided the result will be non-negative</u>; it has no effect on any other variable in the information set. The operation has no successor when the semaphore has values less than one. I.e., <u>if</u> s is a semaphore, the operation

$$\underline{\mathbf{s}} = 3 \xrightarrow{Q} \underline{\mathbf{s}} = 2$$

is possible, but the state

is a blocking state of Q. I.e., Q cannot continue to operate until the value of  $\underline{s}$  is changed by some other means.

In this thesis, we will ignore all issues surrounding the decidability or undecidability of whether or not a particular operation  $y_0 \xrightarrow{Q} y_1$  can occur, and we will restrict our attention to processors such that this can be determined for all values  $y_0$  and  $y_1$ .

It may be the case that some value of  $y_0$  of an information set Y has more than one successor under processor Q - i.e., that

$$y_0 \xrightarrow{Q} y_1$$

$$y_0 \xrightarrow{Q} y_2$$

$$\vdots$$

$$y_0 \xrightarrow{Q} y_k$$

and  $y_1 \neq y_2 \neq \ldots \neq y_k$ . I.e., Y does not contain enough information to allow us to determine which operation Q will make next. It may be chosen by a random process or it may depend on factors external to our domain of discourse. In this case, P is called <u>non-deterministic</u>: otherwise it is <u>deterministic</u>. (Note that this use of the term "non-deterministic" is related to, but not the same as, its use by Floyd [1967b]. Ashcroft and Manna [1971] also use the term with slightly different implications.) Although we like to think of the hardware processors which we build as deterministic, we combine them in system with the result, which we will see presently, that abstract processors of operating systems are frequently non-deterministic.

### Processors with Multiple States

It will be convenient to consider processors with more than one internal "state". For example, a processor may be defined by an Algol program and its operand may be the variables of that program. Clearly, the operations defined by this processor depend upon which statement is currently being executed. This is not represented by any part of the operand, but by information strictly internal to the program. I.e., for a given value of the operand, the possible successors are determined by the current internal state of the processor. In general, if a processor P in state  $v_0$  can perform the operation  $y_0 \longrightarrow y_1$  and find itself in state  $v_1$  as a result, we say

$$(y_0, v_0) \xrightarrow{P} (y_1, v_1),$$

i.e., that  $(y_1,v_1)$  is a successor of  $(y_0,v_0)$  under the processor P. The set of internal states of P may represent values of internal registers or data structures, the position of a reel of tape, a program counter, or some other characteristic.

From a theoretical point of view, there is little to distinguish single state processors from multiple state processors, and either kind can be mapped directly to the other kind. I.e., the operand of a multiple-state processor can be extended with an information element representing the states. Then a new, single-state processor can be defined with operations similar to those of the given one and dependent in the obvious way on the new information element. Conversely, a processor with only one or a few states can be transformed into one with many states by moving information from its operand to its internal structure. For convenience,

we will usually assume that our processors can have several states.

In Chapter II a method of representing a class of these will be presented.

### Computation and Processes

When a processor is repeatedly applied to an information set, it defines a sequence of values of that set which is the essence of the computing task for which the two were intended. The sequence may be finite or infinite, and it is called a computation.

<u>Definition</u>: Let P be a processor, and let the information set Y be an operand of P, let  $y_0$  be a value Y, and let  $v_0$  be an internal state of P. A computation of P on Y given  $(y_0, v_0)$  is a sequence of pairs,

$$\{(y_0, v_0), (y_1, v_1), (y_2, v_2), \dots\}$$

either finite or infinite, where for each  $i = 0,1,2,...,y_i$  is a value of Y,  $v_i$  is an internal state of P, and

$$(y_i, v_i) \xrightarrow{P} (y_{i+1}, v_{i+1})$$

The state  $(y_0, v_0)$  is called the <u>initial</u> state of the computation.

Note that if P is non-deterministic, there may be more than one computation for some initial states. Finally note that Horning and Randell [1969] use the term "history" to denote what we have called "computation".

Given an information set Y, a set  $\Sigma$  of initial values of Y, and an effective description of a processor P which operates on Y, it is possible to construct all of the computations of P on Y given any of the initial

values in  $\Sigma$ . This set of computations, called the <u>history set</u> by Horning and Randell, represents all that P can do to Y. All of the values of Y which might conceivably occur, solely as the result of the action of P, are members of the computations in the set, and the set itself is completely determined by P, Y, and  $\Sigma$ . This motivates the following definition.

<u>Definition</u>: A <u>process</u> is a triple  $(P,Y,\Sigma)$ , where

P is a processor,

Y is an operand of P, and

$\Sigma$  is a (non-null) set of pairs (y,v) consisting of values of Y and internal states of P.

We will frequently represent processes by lower case letters

If  $p = (P, Y, \Sigma)$  is a process and if  $(y_0, v_0)$  is in  $\Sigma$ , then a computation of P on Y given  $(y_0, v_0)$  is called a <u>computation of p</u>.

The term "process" is common in operating system design and has been defined in many different, but related, ways. Saltzer's emphasis [1966] is on the activity of the processor and on which information set is involved. Lampson [1968] emphasizes that it is distinct processors which make distinct processes. Dijkstra [1965a] identifies a process as the act of a processor operating on an information set to produce a specific computation. Horning and Randell [1969] have surveyed other definitions. All of them specify, in one way or another, that the principal ingredients of a process are its own processor, an information set, and a starting

state. Brinch Hansen [1970] has emphasized that processes are not restricted to those having processors resembling the central processing units of conventional computers. The asynchronous input/output activities, the ticking of system timers, and the setting of external switches all are types of processes, and all fall within the definition given above.

### Timelessness of Processor Operations

Our definitions of computation and process make no mention of time, but only of ordered sequences of states. Yet they represent activities which occur in time and which take non-infinitesimal time to happen. This important aspect of our model of computation was introduced by Dijkstra [1965a]. It simplifies considerably the analysis of cooperating processes to be considered below; but at the same time, it requires that the processes under scrutiny have a certain kind of structuring about them.

Essentially, what we do is assume that the operations of processors occur in zero time, and that processors and information sets spend all of their time between operations. In effect, time acts as a discrete counter, not as continuous measure (Habermann [1967]). We further assume that no two processors perform operations on information at precisely the same instant. I.e., whenever two processors both perform operations, we assume that one performs its operation of infinitesimal duration first, then the other acts. The order might not be predictable. (In the case of processors specifically designed to work in "lockstep", they can be combined into a single processor by the methods

of synchronous combination discussed by Horning and Randell [1969].)

A consequence of this abstraction is that the value of an information set at the instant after an operation is determined only by the processor which performs it, not on any possible interference by other processors.

No piece of physical machinery actually performs operations in zero time, but most of the processors and storage media that we build today act as if this were true. That is, they are designed with interlocks and interfaces which guarantee that the sequences of observable information states are exactly those which would be observed if a timeless processor were used instead.

Example: The core memories of most modern computer systems are designed so that a CPU and an I/O channel cannot both access a given word simultaneously. One must wait until the other has completed its operation, then it operates on the new value of memory.

It is a non-trivial problem to construct processors which obey this principle and an even harder problem to prove that they do obey it. The operating system programmer can, with some restrictions, assume that his hardware obeys it; but he must write programs which are, in effect, abstract processors which also obey the principle. This has been the subject of considerable discussion in the literature, and it has given rise to the various so-called "synchronizing primitives" which are now common programming practice (see, for example, the P- and V-operations of Dijkstra [1965], the message handling functions of Brinch Hansen [1970], the functions in MULTICS as described by Saltzer [1966]). Thus, an

important verification problem is that of proving that the abstract processors simulated by a set of cooperating processes obey the principle of timelessness.

#### Cooperation Among Processes

Let  $p = (P, Y, \Sigma)$  and q = (Q, Z, T) be processes, as defined previously. Let us consider what happens if  $Y \cap Z$  is not null. That is, we will allow the processor P to access some information elements in Z and Q to access some elements in Y. Clearly, the sequences of states of Y and Z realizable by this case are not necessarily computations of p and q, but may be the result of interactions between the two processors. For example, P may change the value of an information element in  $Y \cap Z$  upon which the next operation of Q depends; such a variable is called a significant variable of Q by Horning and Randell [1969].

In order to see what sequences of states of Y  $\cup$  Z are possible, we will construct a processor R from the definitions of P and Q. For simplicity, let us first assume that P and Q have only one internal state each. Then we define the single state processor R as follows:

whenever  $y_a \cup z_a$  and  $y_b \cup z_b$  are values of  $Y \cup Z$ , then

$$y_a \cup z_a \xrightarrow{R} y_b \cup z_b$$

if and only if either

$$y_a \xrightarrow{P} y_b$$

and  $z_a \setminus y_a = z_b \setminus y_b$

or

$$z_a \xrightarrow{Q} z_b$$

and  $y_a \setminus z_a = y_b \setminus z_b$

I.e., an operation of R on Y  $\cup$  Z is either an operation of P on Y with that part of Z which does not intersect with Y (Z  $\setminus$  Y) left unchanged, or it is an operation of Q on Z with Y  $\setminus$  Z left unchanged.

In general, R is not deterministic because there can be values of Y U Z which are not blocking states for either P or Q. For these states, the choice of which operation R performs next depends upon the relative speeds of P and Q, the physical implementation of the processors and information sets, and/or other factors which may be random or imperceivable.

In order to define a process based on R and Y  $\cup$  Z, we must also define a set of initial states of this information set. In particular, let  $\nu$  be the set of values

$$\{y \cup z \mid y \in \Sigma \text{ and } z \in T\}.$$

I.e., it is the set of values of Y  $\cup$  Z such that the Y-part is an initial state of <u>p</u> and the Z-part is an initial state of <u>q</u>. In symbols, we say  $\upsilon = \Sigma * T$ . Then, by construction, the computations of the process

$$\underline{\mathbf{r}} = (\mathbf{R}, \mathbf{Y} \cup \mathbf{Z}, \mathbf{v})$$

are exactly the sequences of values of Y  $\cup$  Z which result from an arbitrary interleaving of the operations of P and Q, subject to the assumption of timelessness. We called the processor R the <u>product</u> of P and Q, and similarly, we call  $\underline{r}$  the <u>product</u> of  $\underline{p}$  and  $\underline{q}$ ; in symbols, we write

$$R = P \times Q$$

and

$$\underline{r} = \underline{p} \times \underline{q}$$

Example: The OS/360 operating system for the IBM System/360 [1970b] defines one or more abstract processes (called tasks in the terminology of that system) which are, in effect, product processes. Each task includes one "computing" process, zero or more "input-output" processes, and zero or more "timer" processes. The computing process is the only one that is programmable in the conventional sense, the others being table-driven. All of the processors are simulated by a combination of the hardware and system software. They communicate using operations on information contained in shared tables for example, the computing processor performs "GET" and "PUT" operations which manipulate and test specific variables, while the input-output processors keep buffers full (or empty) and record their status in those same variables. The system programmer generally regards a whole task as a programmable process, but he must be aware of the non-determinism of the synchronization among the component processes. I.e., a task is a product of simpler processes.

In the case of processors with more than one internal state we can formulate the notion of product precisely as follows:

- <u>Definition</u>: If P is a processor of the information set Y and Q is a processor of the information set Z, then the <u>product</u>, R, of P and Q is a processor of the information set  $Y \cup Z$  such that

- (a) the set of internal states of R is the set of pairs  $\{(v,w)\}$  where v is an internal state of

P and w is an internal state of Q, and

(b) for values  $y_a \cup z_a$  and  $y_b \cup z_b$  of  $Y \cup Z$  and for states  $(v_a, w_a)$  and  $(v_b, w_b)$  of R,  $(y_a \cup z_a, (v_a, v_w)) \xrightarrow{R} (y_b \cup z_b, (v_b, w_b))$  if and only if <u>either</u>  $(y_a, v_a) \xrightarrow{P} (y_b, v_b) \text{ and } z_a \setminus y_a = z_b \setminus y_b$  and  $w_a = w_b$

$\frac{\text{or}}{(z_a, w_a)} \xrightarrow{Q} (z_b, w_b) \text{ and } y_a \setminus z_a = y_b \setminus z_b$ and  $v_a = v_b$ .

The <u>product</u>, <u>r</u>, of two processes  $p = (P,Y,\Sigma)$  and q = (Q,Z,T) is the process  $(R,Y \cup Z,\upsilon)$ , where  $\upsilon = \Sigma * T$ . In symbols, we write

$$R = P \times Q$$

$$\underline{r} = \underline{p} \times \underline{q}.$$

and

Informally, we say that the processes p and q cooperate and communicate through their common information set  $Y \cap Z$ .

Clearly it follows from that definition and the commutativity of set union that the processors  $P \times Q$  and  $Q \times P$  define exactly the same set of operations on  $Y \cup Z$ , and so can be considered the same processor. It is also apparent from the construction that the processors

$$P \times (Q \times R)$$

and

$$(P \times Q) \times R$$

are identical.

Note that according to the definition, a processor cannot force a change in internal state upon another. There is no practical loss of generality here because the representation can be changed so that the internal states are described by information elements common to the operands of both processors.

Finally observe that since by our definition the combination of a set of processes is also a process, we could use the term "process" to mean a single, deterministic process or the combination of a set of processes. However, it will sometimes be advantageous to talk about a "system of processes" in order to make it clear that we are interested in properties relating to the combination of the processes and not specific to any individual one.

## A Characterization of Operating Systems

Randell [1971], paraphrasing Barron [1969], has observed that while it is difficult to define precisely what we mean by the term "operating system", any experienced programmer would recognize one when he sees it. Nevertheless, we can characterize operating systems with respect to certain properties relevant to specific problems. For example, a person interested in performance might characterize all operating systems as resource allocation mechanisms, while someone else might characterize them as interpreters of command languages. From the point of view of an abstract study of correctness, we can regard an operating system as a collection of processes which cooperate to simulate one or more abstract processors and information sets. I.e., using a common but imprecise term, we regard an operating system as a collection of processes

which create one or more "virtual machines". The programs of an operating system collectively act as interpreters of the abstract processes so created. The question is then, "Do the processes correctly simulate what they are designed to simulate?".

There are several important characteristics of these programs which affect the problem of proving them correct. One is that many of them are not meant to terminate, so that verification techniques based on termination do not apply. I.e., these programs, particularly those that manage the processors and principal memory resources, loop and repeatedly look for work to do. They also transmit information from one iteration to another, so that there is no natural terminating point.

Another characteristic of programs in operating systems is that they define, communicate with and synchronize with other processes.

I.e., they transmit information to others via shared data, and they await answers. They become blocked by menas of synchronizing operations such as the P- and V-operations or their equivalent. Thus there are the natural questions of whether or not they communicate and synchronize correctly, and whether they will be restarted correctly when they are blocked pending some event.

A third characteristic is that, despite the best intentions of operating systems programmers, the processes are at times non-deterministic. Processes are combined with others to form product processes which are non-deterministic, at least to the extent of the relative speeds of the components. This complicates the verification problem because the values of shared variables are not necessarily safe - i.e.,

one process may set a value but another may change it at any time.

These considerations will motivate the verification methods introduced in later chapters. It will be apparent that they also apply to other systems of cooperating processes which are not operating systems. However, we shall restrict our attention and examples to problems drawn from the operating system area.

#### CHAPTER II

#### TRANSITION GRAPHS

In later chapters, a principal method of proving the correctness of a process or product of processes will be to prove that a statement is true for each of its computations. This requires a representation of processes and processors which facilitates systematic proofs about all computations, possibly infinitely many of them. A suitable representation for this purpose is the directed graph used by Manna [1968] which, for lack of a better term, we will call the transition graph. It is analogous to a flowchart, but the roles of nodes and arcs are interchanged, the arcs representing actions and nodes representing the intervals between actions.

In this chapter, the idea of the transition graph will be illustrated by a brief example and then defined precisely. We will show that it represents all of the computations of the corresponding process. We will also present a natural way of combining transition graphs of several processes which results in a transition graph representing the product of those processes. This is convenient for considering the computations which result from the cooperation of several processors operating on a common information set. Finally, we will comment on some useful properties of transition graphs.

#### Transition Graph of a Process

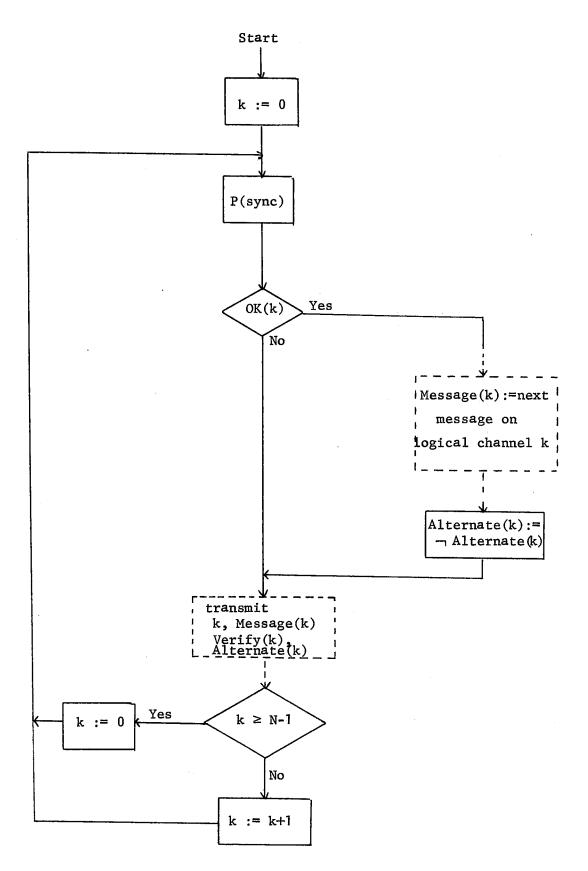

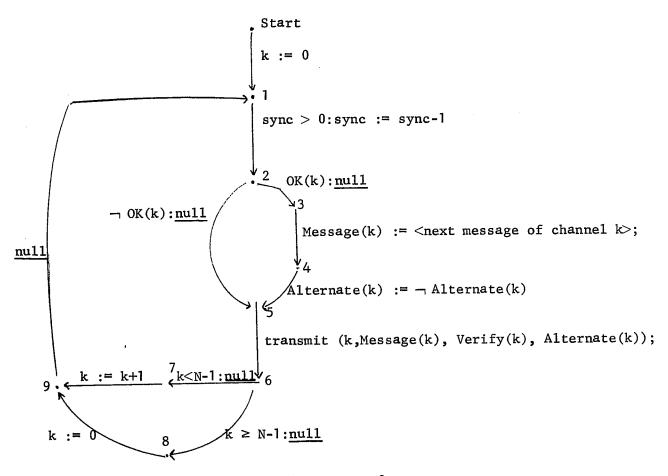

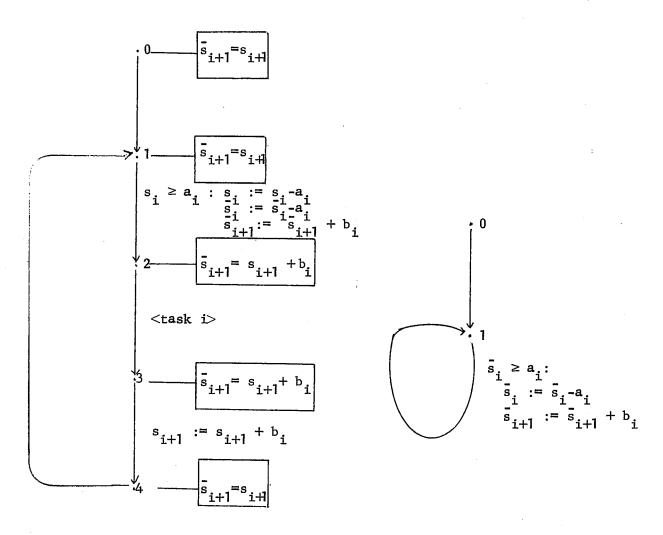

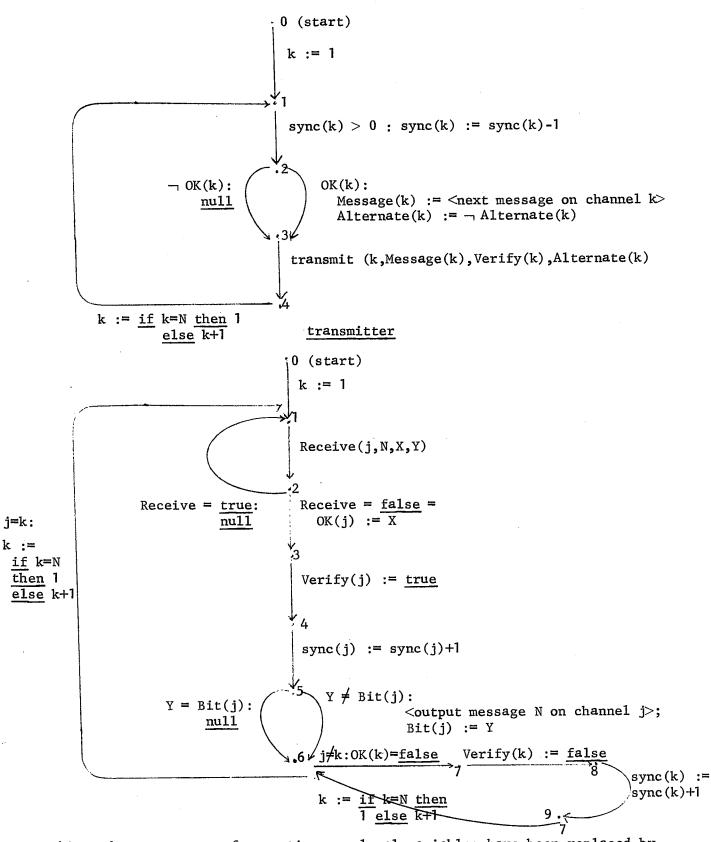

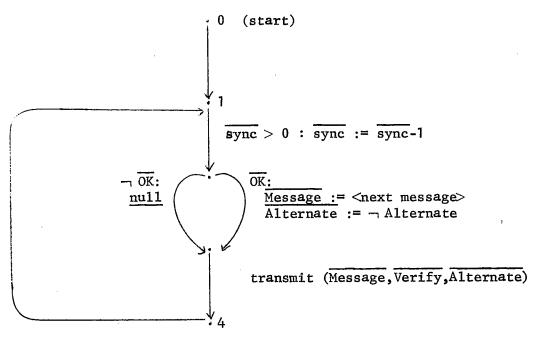

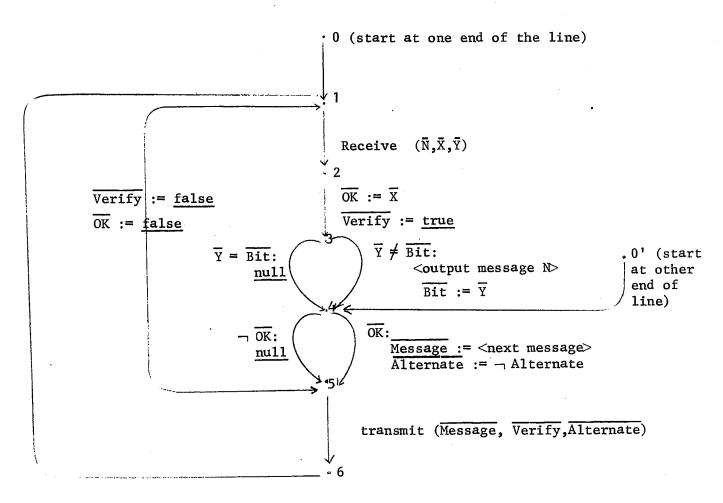

Let us consider a process designed to multiplex and transmit messages of N "logical" communication channels over one physical communication channel. This process will be part of a system for reliable and efficient communication, proposed by Lynch [1968 and 1971] and to be discussed in Chapter V. The processor and its information set can be described by the pseudo-Algol program of Figure II.1. The process continually loops, transmitting the messages contained in its buffer named "Message". If "OK" indicates that a message has been correctly received, a new message is fetched from the corresponding logical channel and the value of "Alternate" is reversed. The physical message actually transmitted consists of the identification "k", the k<sup>th</sup> message, and the values of the k<sup>th</sup> Verify and Alternate bits.

In Figure II.2, a flowchart of the program is shown. It is reasonable to expect that each solid box in the flowchart could correspond to one, indivisible, timeless operation by a suitable processor. The dotted boxes, however, represent operations which would probably be implemented as several operations spanning a non-trivial amount of time. But for purposes of illustration, we will imagine them to be timeless operations, as well.

```

begin string array Message (0:N-1);

Boolean array OK (0:N-1) = \underline{true};

Boolean array Verify, Alternate (0:N-1) = false;

semaphore sync=N; integer k;

comment: The string array "Message" contains the

current messages being transmitted on the

logical channels. "OK" is set by another pro-

cess to indicate that messages have been re-

ceived correctly. "Verify" and "Alternate"

will be explained later. The semaphore "sync"

is used for synchronizing this process with

another one;

for k := 0, (if k \ge N-1 then 0 else k+1) while true do

begin P(sync);

if OK (k) then begin

Message (k) := <next message on channel k>;

Alternate (k) := \neg Alternate (k) end;

transmit (k, Message (k), Verify (k),

Alternate (k)); end;

end;

```

Figure II.2

In Figure II.3, we show a transition graph representation of the same processor. The boxes of the flowchart have been replaced by labeled arcs and the lines of the flowchart have been replaced by nodes. Some of the labels on the arcs have two components separated by a colon: a condition and an action. The condition is a predicate on the values of variables of the process which, if true, allows control to "follow" that arc. The remaining labels have only one component, an action. The action is either <u>null</u> or an assignment to one or more variables of the process; it represents an operation of the processor. For example, the box of Figure II.2 which performs the operation "P(sync)" corresponds

Figure II.3

to the arc between nodes 1 and 2 in Figure II.3 and is labeled with a predicate representing the condition

sync > 0

and action

sync := sync-1.

The test and the action are assumed to take place simultaneously and in infinitesimal time.

Each node of the transition graph represents an internal state of the processor described by the program, and each arc leading from a node represents an operation or class of operations which can occur when the processor is in the corresponding state. Thus it is possible to construct computations of the process by following paths through the graph and performing the operations indicated by the arcs. A given arc can be included in such a path only if its condition label is true at the time it is encountered. If all of the operations of the processor are represented by the appropriate arcs, then all such paths through the graph correspond to computations. Conversely, every computation of the process corresponds to some path. This can be made more precise by the following construction.

Let <u>p</u> be the process  $(P,Y,\Sigma)$ , and suppose that V, the set of internal states of P, is finite. Let G be a directed graph with labeled arcs such that:

- (a) The nodes of G are the elements of V.

- (b) The arcs are represented by ordered pairs of elements of V and the set of arcs is denoted by  $\Gamma$ .

(c) Associated with each arc  $\langle v,w \rangle$  in  $\Gamma$  is a label consisting of two parts: a predicate  $\phi_{\langle v,w \rangle}(y)$  on the values of Y and a function  $t_{\langle v,w \rangle}(y)$  which maps the set of values of Y into itself. Denote the set of labels by L.

Thus the graph G is a triple  $(V,\Gamma,L)$ .

Definition: The graph  $G = (V, \Gamma, L)$  is a <u>transition graph representation</u>

of the process p if and only if the following is true:

For any values  $y_1$  and  $y_2$  of Y and any elements  $v_1$  and  $v_2$  in V,

$$(y_1,v_1) \xrightarrow{P} (y_2,v_2)$$

if and only if

- (a) there is an arc  $\langle v_1, v_2 \rangle$  in  $\Gamma$ ,

- (b)  $\varphi_{< v_1, v_2>}(y_1) = \underline{\text{true}}, \text{ and}$

(c)

$$y_2 = t_{\langle v_1, v_2 \rangle}(y_1)$$

.

Thus a directed graph of this form is a transition graph representation of a process if and only if its arcs exactly represent the operations of the processor.

In Figure II.3, the action labels were shown as assignments, whereas in the definition they are presented as functions. We will use this "assignment notation" as a useful way of representing functions on the states of information sets, i.e., the assignments describe how the functions operate on the individual elements of an information set. For example, if the set Y consists of the set of elements  $\{a,b,c\}$ , then

the assignment

$$\underline{a} := \underline{b} + \underline{c}$$

is shorthand for the function

$$t(\underline{a},\underline{b},\underline{c}) = \{\underline{b}+\underline{c},\underline{b},\underline{c}\}$$

while the two simultaneous assignments

$$a := 0$$

$$b := a+c$$

are shorthand for the function

$$t'(\underline{a},\underline{b},\underline{c}) = \{0,\underline{a}+\underline{c},\underline{c}\}.$$

Both functions take as arguments states of Y and have values which are also states of Y. Throughout the thesis, we will use the assignment notation when it is convenient, but we will always interpret it as a function.

### Computational Paths

It is now possible to show that paths through a transition graph representing a process correspond to the computations of that process and conversely. Let us define a <u>simple path</u> through a transition graph  $G = (V, \Gamma, L)$  as a sequence of nodes of V,

$$\{v_0, v_1, v_2, \dots\}$$

either finite or infinite, such that for each i=0,1,2,..., there is an arc  $\langle v_i,v_{i+1}\rangle$  in  $\Gamma$ . That is, a simple path is just a way of tracing

through the transition graph by following arcs. A <u>computational path</u> is a sequence of pairs

$$\{(y_0, v_0), (y_1, v_1), (y_2, v_2), \ldots\}$$

of values of Y and elements of V, such that

$$\{v_0, v_1, v_2, ...\}$$

is a simple path  $\phi_{< v_i, v_{i+1}} > (y_i) = \underline{\text{true}} \text{ for all } i = 0, 1, 2, ...$   $y_{i+1} = t_{< v_i, v_{i+1}} > (y_i) \text{ for all } i = 0, 1, 2, ...$

That is, a computational path is a way of tracing through a transition graph while performing the tests and operations indicated by the labels on the arcs.

<u>Lemma II.1</u>: Let  $p=(P,Y,\Sigma)$  be a process, let  $G=(V,\Gamma,L)$  be a transition graph representation of p, and let  $(y_0,v_0)\in\Sigma$ . Then the sequence of pairs

$$\{(y_0, v_0), (y_1, v_1), (y_2, v_2), \dots\}$$

is a computation of  $\underline{p}$  if and only if it is a computational path in G.

Proof: From the definition of transition graph, the operation

$$(y_i, v_i) \xrightarrow{P} (y_{i+1}, v_{i+1})$$

is part of the processor p if and only if

$$\varphi_{\langle v_i, v_{i+1} \rangle}(y_i) = \underline{\text{true}}$$

$$y_{i+1} = t_{\langle v_i, v_{i+1} \rangle}(y_i)$$

for any i = 0, 1, 2, ...,

That is, the operation is part of P if and only if the arc  $v_i, v_{i+1}$  can be included in a computational path. The lemma follows by induction on the length of the sequence.

### Transition Graphs of Combinations of Processes

We are now ready to present the main result of this chapter. Let  $p = (P,Y,\Sigma)$  and  $p' = (P',Y',\Sigma')$  be processes represented by transition graphs  $G = (V,\Gamma,L)$  and  $G' = (V',\Gamma',L')$ , respectively. Let the process  $q = p \times p'$  be the product of p and p' according to the definition of the previous chapter. We will construct a graph  $H = (W,\Lambda,M)$  and show that it is a transition graph representation of q. Then as a consequence of the previous lemma, the set of computations of q will correspond exactly to the set of computational paths in this graph.

To construct H, let the set of nodes W be the set V  $\times$  V' - i.e., the nodes of H are pairs of nodes of G and G'. Let the set of arcs  $\triangle$  and the set of labels M be defined as follows:

(a) for each arc  $\langle v_1, v_2 \rangle$  of  $\Gamma$  with label

$$\varphi_{< v_1, v_2>}(y): t_{< v_1, v_2>}(y)$$

and for each node v' of V', let an arc

$$< w_1, w_2 > = < (v_1, v'), (v_2, v') >$$

be included in ∆ and labeled by

$$\theta_{< w_1, w_2>}(y \cup y') : u_{< w_1, w_2>}(y \cup y')$$

where

$$\theta_{<\mathbf{w}_{1},\mathbf{w}_{2}>}(y \cup y') = \phi_{<\mathbf{v}_{1},\mathbf{v}_{2}>}(y)$$

$$\mathbf{u}_{<\mathbf{w}_{1},\mathbf{w}_{2}>}(y \cup y') = \mathbf{t}_{<\mathbf{v}_{1},\mathbf{v}_{2}>}(y) \cup (y' \setminus y)$$

(b) symmetrically, for each arc  $\langle v_1', v_2' \rangle$  of  $\Gamma'$  with label

$$\phi'_{\langle v_1', v_2' \rangle}(y'):t'_{\langle v_1', v_2' \rangle}(y')$$

and for each node v of V, let an arc

$$\langle \bar{w}_1, \bar{w}_2 \rangle = \langle (v, v_1'), (v, v_2') \rangle$$

be included in ∆ and labeled by

$$\bar{\theta}_{<\bar{w}_{1},\bar{w}_{2}>}(y \cup y'): u_{<\bar{w}_{1},\bar{w}_{2}>}(y \cup y')$$

where

(c) no arcs are included in  $\Delta$  except by virtue of (a) or (b). That is, each arc of G has a corresponding arc in H for every node of G' and each arc of G' has a corresponding arc in H for every node of G. The condition and action labels on the arcs of H are exactly the same as those on the corresponding arcs of G and G', but defined in terms of the information set union Y  $\cup$  Y'. Thus the condition  $\theta_{\langle w_1, w_2 \rangle}$  on arc  $\langle w_1, w_2 \rangle = \langle (v_1, v'), (v_2, v') \rangle$  above is a predicate on values of Y  $\cup$  Y' which is equal to  $\phi_{\langle v_1, v_2 \rangle}$  defined on the values of the Y-component only. Similarly, the function  $u_{\langle w_1, w_2 \rangle}$  denotes an operation on the value Y  $\cup$  Y' equal to the operation defined by

$t_{< v_1, v_2>}$  on values Y, leaving that part of Y' not in the intersection unchanged. Note that the assignment notation discussed above simplifies the labels on arcs of H considerably.

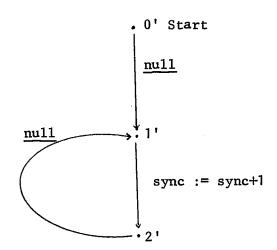

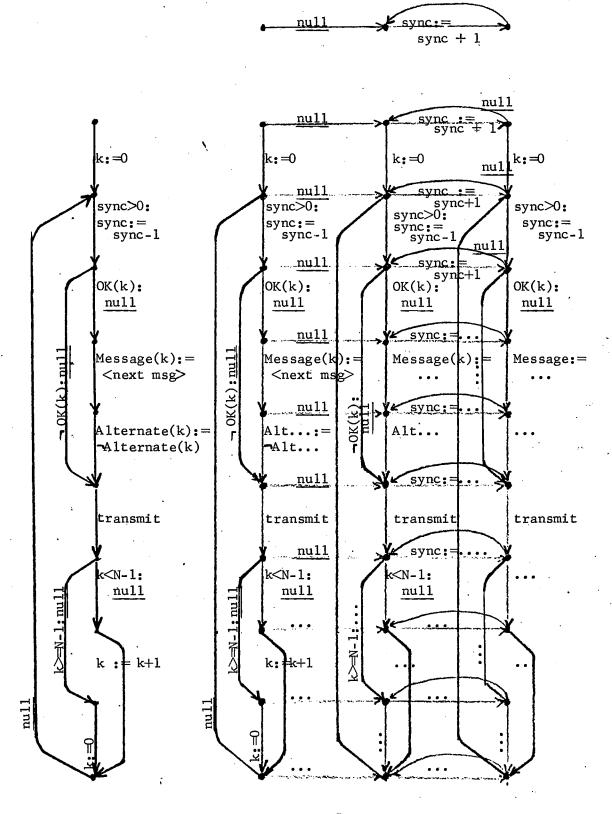

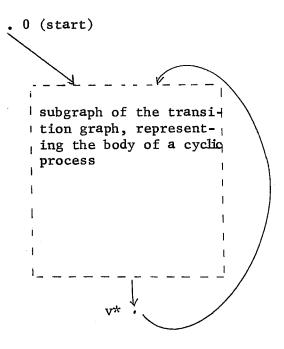

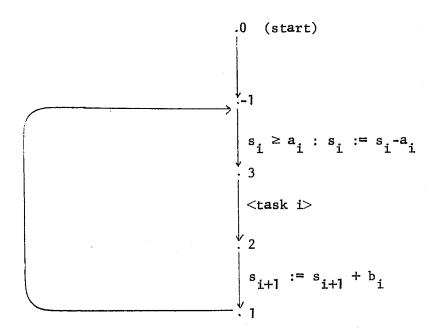

We can see intuitively how the graph H is formed from an example. Figure II.4 shows transition graph G' representing a small, useless process which cooperates with that of graph G of Figure II.3. Figure II.5 shows the "product" H of these two transition graphs. Along the side of the figure is a copy of G, stretched out in a "linear" form; and similarly G' is depicted at the top of the figure. Some of the labels are omitted or abbreviated where they can be deduced from context. H is essentially formed from a copy of G for each node of G' "crossed" with a copy of G' for each node of G. Note that from most nodes, there are two arcs which can be followed at any given time. This reflects the natural non-determinacy of two processes in which an operation of either processor might be executed next. The paths through the graph intuitively reflect the computations which can result from the two processors working together. This conclusion is based, in part, on the next lemma.

- <u>Lemma II.2</u>: The directed graph H constructed above is a transition graph representation of the process  $q = p \times p'$ .

- <u>Proof:</u> Note that W, the set of nodes of the graph H, is exactly the set of pairs of internal states of P and P', which is also the set of internal states of Q by the definition of product processor in Chapter I. Thus, H is a transition graph representation of q if and only if there is an exact correspondence

The transition graph G' representing a simple process

## Figure II.4

between the arcs in  $\Delta$  and the operations or classes of operations in Q. Suppose that

(1)

$$(y_1 \cup y_1', (v_1, v_1')) \xrightarrow{Q} (y_2 \cup y_2', (v_2, v_2'))$$

and suppose that this is true because

(2)

$$(y_1,v_1) \xrightarrow{P} (y_2,v_2)$$

,

with  $v_1' = v_2'$ , and  $y_1' \setminus y_1 = y_2'$ . I.e., suppose the operation (1) has been included in the product processor Q because it is part of the component processor P (a symmetric argument would apply for P'). Then since G is a transition graph representation of P, there is an arc  $\langle v_1, v_2 \rangle \in \Gamma$  such that

$$\varphi_{< v_1, v_2>}(y_1) = \underline{\text{true}}$$

and

$$y_2 = t_{< v_1, v_2>}(y_1)$$

Thus, by construction of H, there is an arc

$$<(v_1,v_1'),(v_2,v_2')> = < w_1,w_2>$$

nu11

Figure II.5

(since  $v_1' = v_2'$ ) in  $\triangle$  with

$$\theta_{\langle w_1, w_2 \rangle}(y_1 \cup y_1') = \underline{\text{true}}$$

and

$$y_2 \cup y_2' = u_{< w_1, w_2>}(y_1 \cup y_1').$$

Conversely, suppose <w<sub>1</sub>,w<sub>2</sub>> is an arc of  $\triangle$  with label

$$\theta_{< w_1, w_2>}(y \cup y') : u_{< w_1, w_2>}(y \cup y')$$

and suppose  $y_1 \cup y_1'$  is any value of  $Y \cup Y'$ , with  $\theta_{< w_1, w_2>}(y_1 \cup y_1') = \underline{\text{true}}$ . Then there is a corresponding arc in either  $\Gamma$  or  $\Gamma'$  - say  $\Gamma$  since the argument is symmetrical for  $\Gamma'$  - such that

$$= <(v_1, v'), (v_2, v')>,$$

$< v_1, v_2> \in \Gamma,$

and

$$\varphi_{}: t_{< v_1,v_2>}$$

is the label on this arc. Thus, by construction,

$$\varphi_{< v_1, v_2>}(y_1) = \underline{\text{true}};$$

and furthermore the operation

$$(y_1,v_1) \xrightarrow{P} (t_{\langle v_1,v_2 \rangle}(y_1),v_2)$$

is part of P, since G is a transition graph representation of p. Thus, the operation

$$(y_1 \cup y_1', (v_1, v')) \xrightarrow{Q} (t_{< v_1, v_2>} (y_1) \cup (y_1' \setminus y_1), (v_2, v'))$$

is part of the product processor. Since by construction

$$u_{< w_1, w_2>}(y_1 \cup y_1') = t_{< v_1, v_2>}(y_1) \cup (y_1' \setminus y_1).$$

this is exactly the operation

$$(y_1 \cup y_1', w_1) \xrightarrow{Q} (u_{< w_1, w_2>} (y_1 \cup y_1'), w_2).$$

Thus the definition of transition graph is satisfied and H is a transition graph representation of the process  $\mathbf{q}_{\bullet}$

We have shown that we can construct a transition graph representing two cooperating processes from the transition graphs representing each one individually. In keeping with previous notation, we can say

$$H = G \times G'$$

Clearly, this product operation is both commutative and associative, just as the product operation on processes is. That is, graphs  $G \times G'$  and  $G' \times G$  are indistinguishable for our purposes, as are  $G \times (G' \times G'')$  and  $(G \times G') \times G''$ .

#### Comments

The transition graph representation of a process will be used to facilitate proving statements about all of the computations of a process. Note that such a representation is not necessarily unique, but that Lemma II.1 guarantees that all transition graphs representing the same process have exactly the same set of computational paths. Furthermore, because of the correspondence between operations of a processor

and arcs of a transition graph, the latter can be used as a definition for the former.

Without loss of generality, we can assume that transition graphs (and their corresponding processors) have at most one node designated as a start node and at most one halt node. That is, a processor and information set can easily be redefined so that this is true without effectively changing the computations it can make or the way it cooperates with other processors. Similarly, we can assume that we can delete arcs with identically false conditions and subgraphs which are never on any simple path beginning at the start node. This is because no action of any processor can force the given processor to traverse such arcs or enter states represented by such subgraphs.

There is one important situation in operating system programming which is not conveniently represented by our model of computation and by transition graphs. This is the interruptible processor, i.e., the processor which can have a forced transfer of control imposed upon it by another. However, this is not a serious restriction if the interrupt handler and the "interruptible" process are two separate, cooperating processes, each with its own abstract processor. The interrupt handler would effectively be a loop with a blocking state which is unblocked whenever the interrupt condition occurs. The non-determinacy of the interrupt system is then represented by the cooperation of two processes. This approach is in keeping with efforts to rationalize interrupt systems by imposing some process structure on them (see, for example, Wirth [1969]).

#### CHAPTER III

#### PROVING CORRECTNESS OF COOPERATING PROCESSES

The statement "Program A is correct" can have many meanings. Intuitively, the most common of these attempt to convey the idea that the program does what the designer intends it to do and/or that the thing he intends is the "right" thing in the context of the problem to be solved. Deciding what algorithm is the right one for a problem is, of course, one of the fundamental aspects of the art and science of programming. Determining whether a particular program in a particular language is an effective representation of an algorithm is a non-trivial problem outside the scope of this thesis.

We can, however, consider a more restrictive concept: "Program A is correct with respect to the statement S". In this case, S is a precise, effective, and meaningful statement characterizing the function of the program. Such statements can take many forms. For example, in Knuth [1969], p. 318, we find the statement "...Algorithm T traverses a tree of n nodes in postorder", where the terms "traverse" and "postorder" had been defined previously. In Dijkstra [1965a], we find the statements

- (a) that at any moment, at most one of the processes is engaged in its critical section;

- (b) that the decision which of the processes is the first to enter its critical section cannot be postponed to eternity;

- (c) that stopping a process in its "remainder of cycle" has no effect upon the others.

Van Horn [1966] considers one criterion of correctness in non-deterministic processes to be "output-functionality" - i.e., that the output of a process is a function only of its inputs and is independent of the behavior of other processes. Each of these statements is meaningful in the sense that it is possible to conceive arguments which could confirm or deny them and that it is possible to draw useful conclusions from them. On the other hand, the statement "This compiler compiles programs correctly" is hardly meaningful without a supporting theory about what correct compilation is and how to do it (see, for example, Good and London [1970]).

In this chapter we will consider the type of correctness criteria introduced by Floyd [1967] and subsequently used by Cooper [1968], Manna [1968], King [1969], London [1970], and others. Statements of correctness assert some relationship among the variables of the process during computation, and the process is considered correct if the statements are true for each computation of that process. These statements, called <u>assertions</u>, are typically associated with lines of the flowchart, nodes of the transition graph, or statements of the program representing the process (although Manna and Pnuelli [1970] have generalized upon this). The assertions take the form of predicates on the values of the process variables which say something about their "meaning". For example,

a = b+3

asserts a clear relationship between the values of the variables <u>a</u> and <u>b</u> which is alleged to be true for every computation when the process is executing the corresponding statement of the flowchart, graph, or program. Assertions specified in this manner can be considered a form of redundancy in programming. That is, the designer specifies an algorithm in a programming language and then a second time (usually incompletely) as a collection of predicates describing the states of the information set. Proving that the process is "correct" with respect to the assertions, then, amounts to showing the mutual consistency of these two specifications. More often than not, both will contain bugs in their initial form. However, we will see that the nature and difficulty of certain kinds of bugs is different in the two characterizations.

In this chapter we will consider assertions about cooperating processes. The Induction Theorem of Floyd [1967] will be applied to verify such processes with respect to these assertions, using the product transition graph representation from the previous chapter. It will be apparent that any attempt to verify a product process this way will be too cumbersome to be practical. However, certain simplifications can be derived from the structure of the components. This chapter concludes with a presentation of some of these techniques and an example of their application.

### Assertions and the Induction Theorem

In order to present these results we will use the following notation and terminology.

<u>Definition</u>: Let  $p = (P,Y,\Sigma)$  be a process represented by transition graph  $G = (V,\Gamma,L)$ . An <u>assertion</u> associated with a node  $v \in V$  is a predicate on the values of Y. The process p is <u>correct</u> with respect to the <u>assertion</u>  $\alpha_V$  if and only if for each state (y,v) which occurs in a computation of p,

$\alpha_{\mathbf{v}}(\mathbf{y}) = \underline{\mathbf{true}}.$

The process p is <u>correct with respect to a set of assertions</u> if and only if it is correct with respect to each assertion in the set.

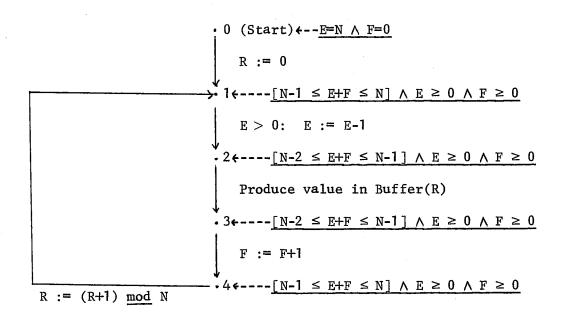

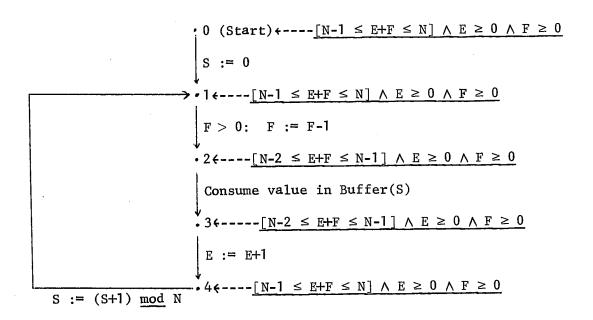

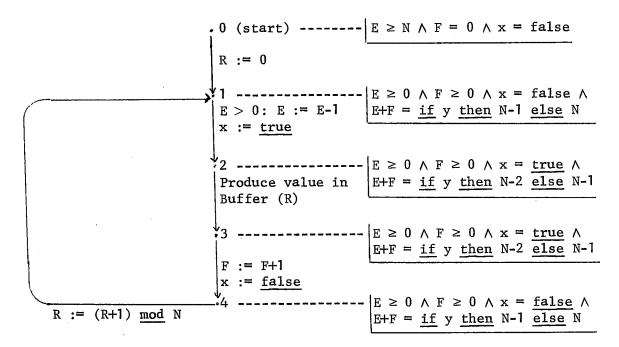

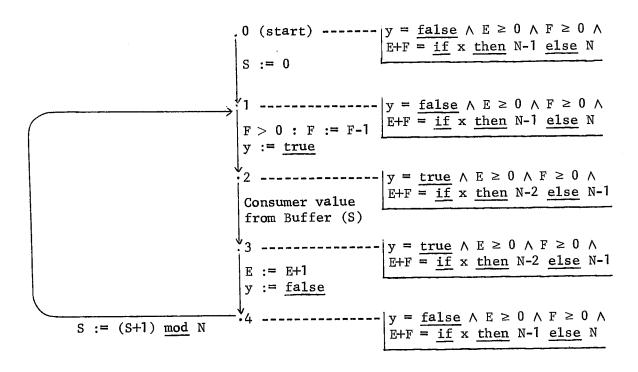

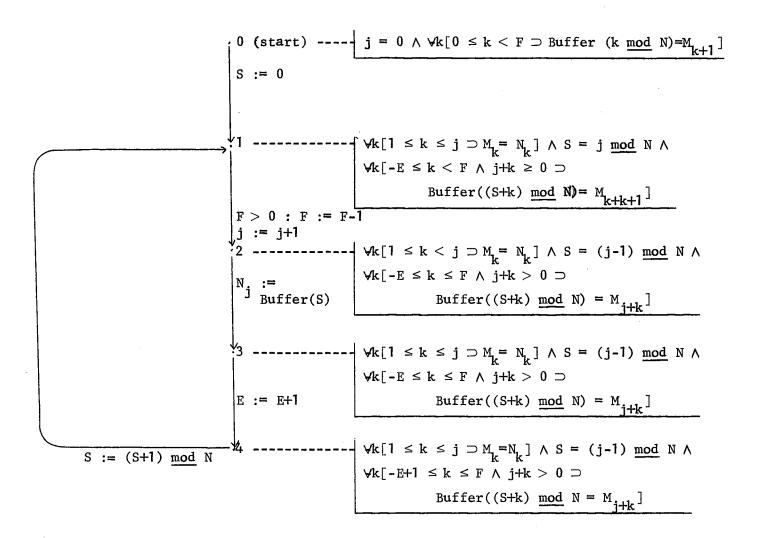

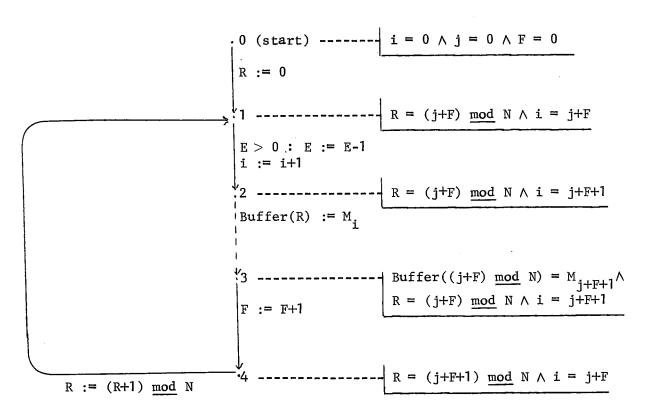

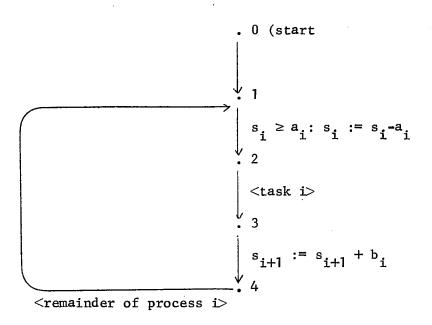

Example: Figure III.1(a) shows a "producer" and a "consumer" process designed to communicate through a ring buffer of N elements.

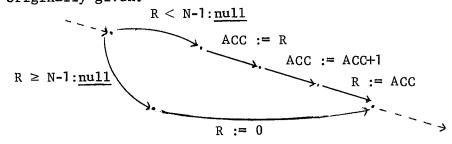

(The parallel block structure notation of Dijkstra [1965a] is used here. Each statement between the parbegin-parend brackets is considered to define a separate processor, and the operand of that process consists of the variables declared on the normal scope of the corresponding statement or its parts.) Synchronization is achieved with two semaphores, E indicating the number of empty buffers and F indicating the number of full buffers. Figure III.1(b) shows a transition graph representation of the producer with assertions attached to its nodes.

At node 1 we have asserted that the sum of semaphores E and F is either N-1 or N and that each is non-negative. At node 2 we have asserted that the sum of E and F is either N-2 or N-1. Similar assertions are applied to each node of the transition graph. If these assertions are true for every computation of the producer (i.e., for every computational path of Figure III.1(b)), then that process is considered correct with respect to them.

```

parbegin semaphore E=N, F=0;

array buffer(0:N-1);

Producer Process: begin integer R;

for R := 0, (R+1)mod N while true do

begin P(E);

produce value in buffer(R)>;

V(F) end;

end;

Consumer Process: begin integer S;

for S := 0, (S+1)mod N while true do

begin P(F);

<consume value from buffer(S)>;

V(E) end;

end;

end;

parend;

```

Algol-like description of Producer and Consumer

# Figure III.1(a)

Transition graph of the Producer

Figure III.1(b)

Transition graph of the Consumer

### Figure III.1(c)

Now consider a set A consisting of assertions for each of the nodes of a transition graph G - i.e.,

$$A = \{\alpha_{\mathbf{v}}(\mathbf{y}) \mid \mathbf{v} \in \mathbf{V}\}.$$

Let  $y_1$  be an arbitrary value of the information set Y, let  $\langle v_1, v_2 \rangle$  be an arbitrary arc in the set  $\Gamma$ , and let  $\phi_{\langle v_1, v_2 \rangle}$ :  $t_{\langle v_1, v_2 \rangle}$  be its label. Suppose that the truth of the assertion  $\alpha_v(y_1)$  and of the condition label  $\phi_{\langle v_1, v_2 \rangle}$  (y<sub>1</sub>) implies the truth of the assertion  $\alpha_v$  on the new value of Y, that is, the truth of  $\alpha_{v_2}(t_{\langle v_1, v_2 \rangle}(y_1))$ . If this assumption were true for all values of Y and all arcs in  $\Gamma$  and if the assertion for every initial state is true, then we could infer by induction the truth of all assertions on all states which occur in computations.

This can be expressed as a well-formed formula of logic as follows:

$$(1) \quad [\alpha_{v_1}(y_1) \land \phi_{< v_1, v_2>}(y_1)] \supset \alpha_{v_2}(t_{< v_1, v_2>}(y_1))$$

For example, if arc  $\langle v_1, v_2 \rangle$  is the arc  $\langle 1, 2 \rangle$  of Figure III.1(b), then (1) becomes

$$\alpha_1$$

: [[N-1  $\leq$  E+F  $\leq$  N]  $\wedge$  [E  $\geq$  0]  $\wedge$  [F  $\geq$  0]  $\wedge$   $\phi_{<1,2>}$ : [E  $>$  0]]  $\supset$   $\alpha_2 \circ t_{<1,2>}^*$ : [[N-2  $\leq$  (E-1) + F  $\leq$  N-1]  $\wedge$  [(E-1  $\geq$  0]  $\wedge$  [F  $\geq$  0]].

Note that in the right side of the implication the new value of <u>each</u> variable is inserted wherever that variable appears in Figure III.1(b); in this case, (E-1) appears for each instance of E and F is unchanged.