# Intel Core i7 Memory Hierarchy

Amanda Adkins, Brett Ammeson, James Anouna, Tony Garside, Lukas Hunker, Sam Mailand

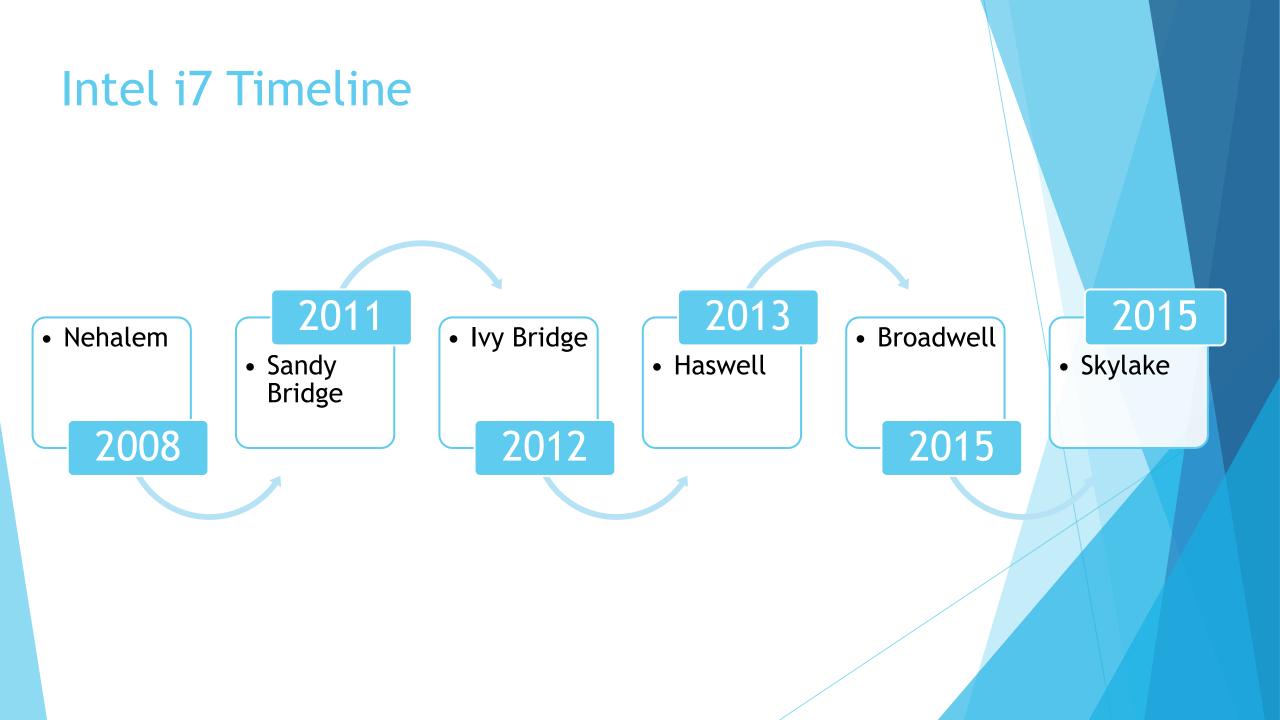

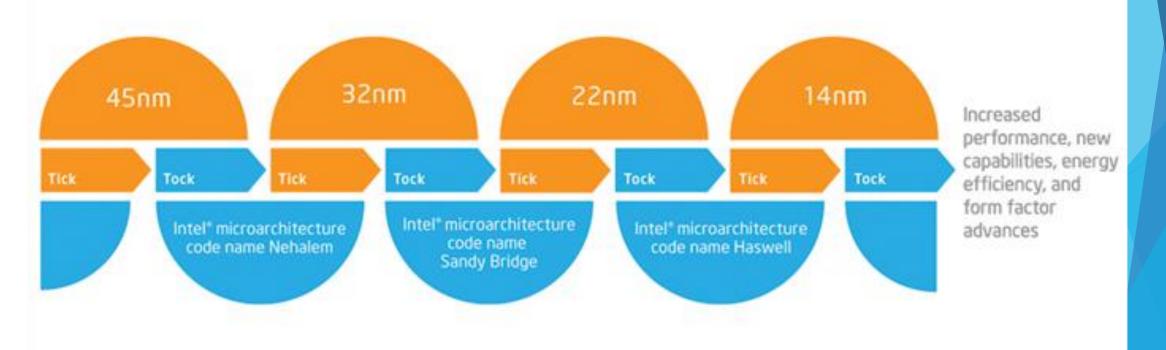

Manufacturing process technology

Microarchitectures

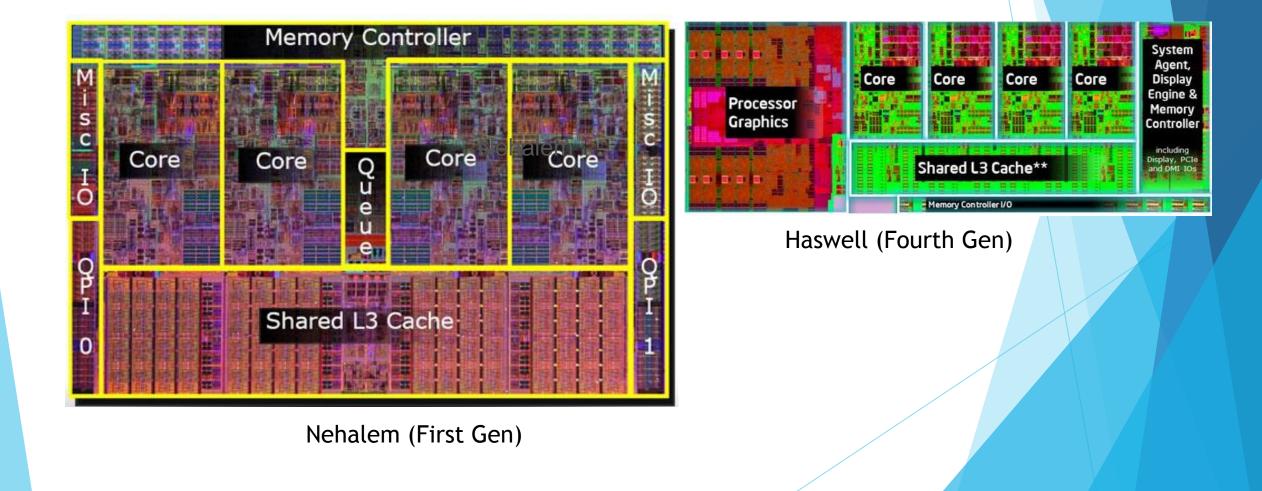

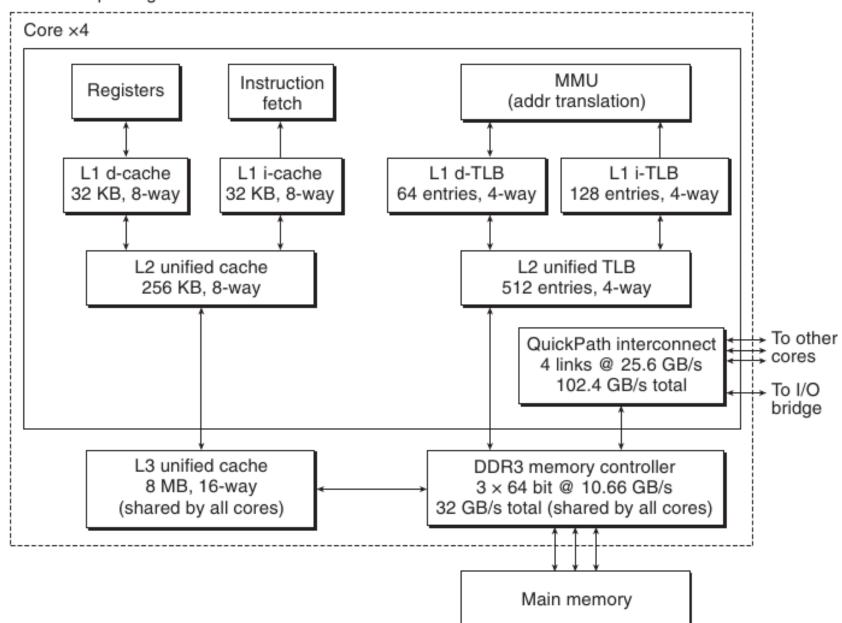

## Core i7 Basic Structure

- 4 cores

- Hyper threaded 8 threads

- Pipelined with 16 stages

# Footprint

# Major Developments

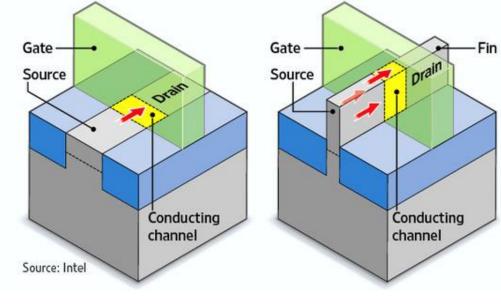

## Intel's Move Into 3-D

The chip maker breaks from conventional approaches to make transistors.

#### **Conventional transistor:**

Electrons flow between components called a **source** and a **drain**, forming a two-dimensional **conducting channel**. A component called a **gate** starts and stops the flow, switching a transistor on or off. Intel's new transistor: A fin-like structure rises above the surface of the transistor with the gate wrapped around it, forming conducting channels on three sides. The design takes less space on a chip, and improves speed and reduces power consumption.

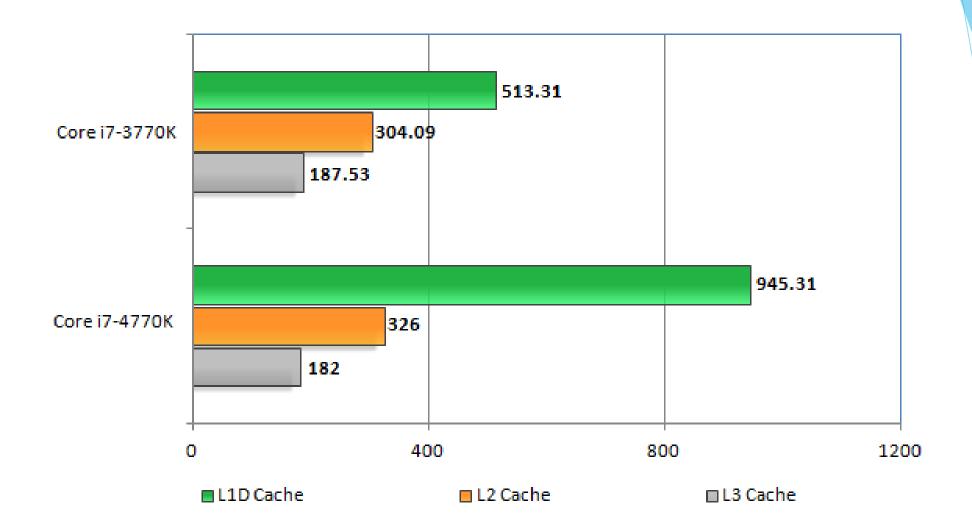

## Increased Cache Bandwidth

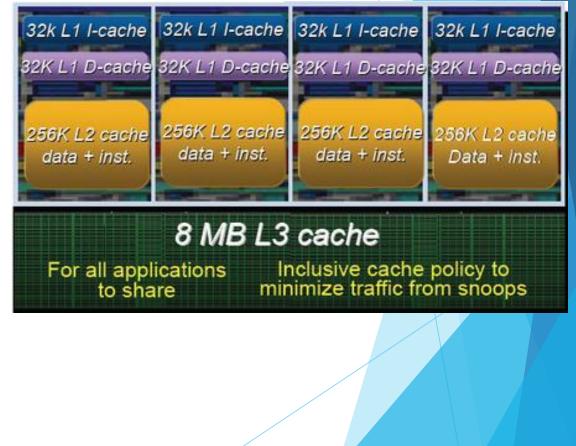

# Intel Core i7 Caching Basics

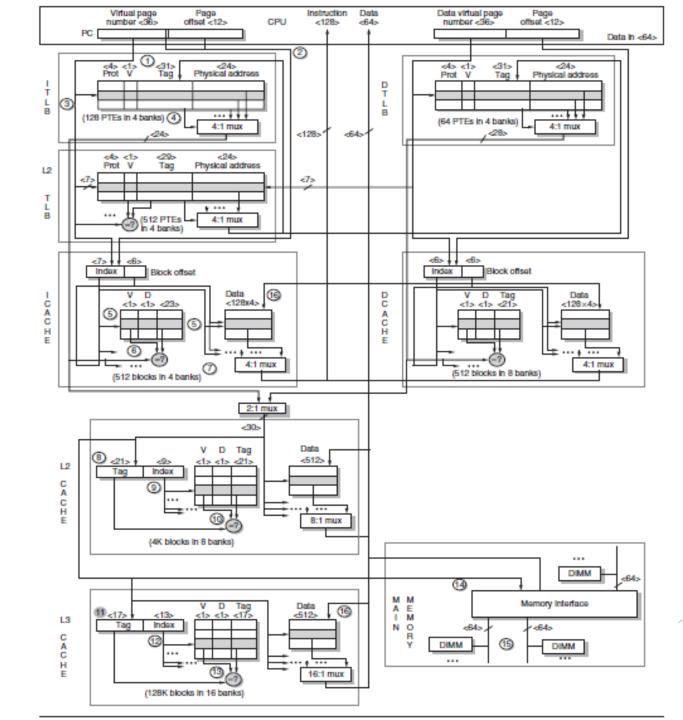

- Intel core i7 processors feature three levels of caching.

- Separate L1 and L2 cache for each core.

- L1 cache broken up into to halves, instruction/data.

- L3 cache shared among all cores and is inclusive.

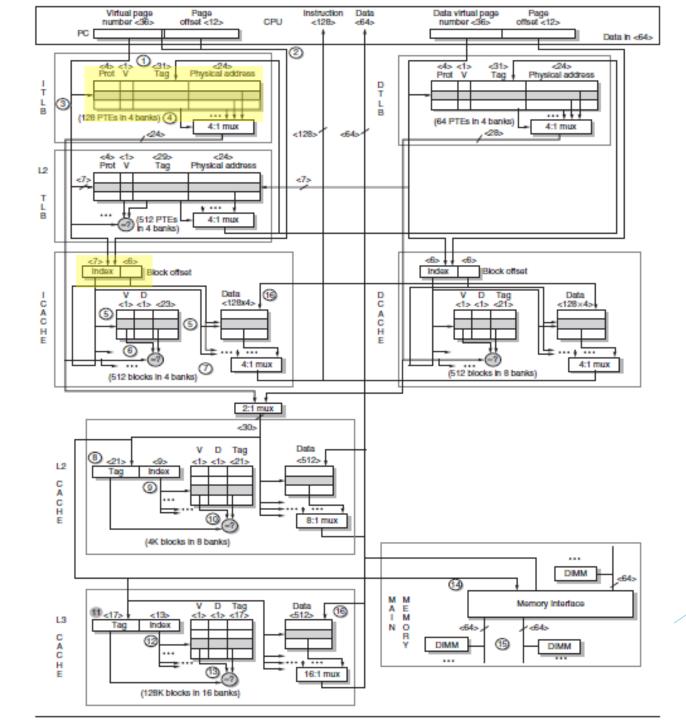

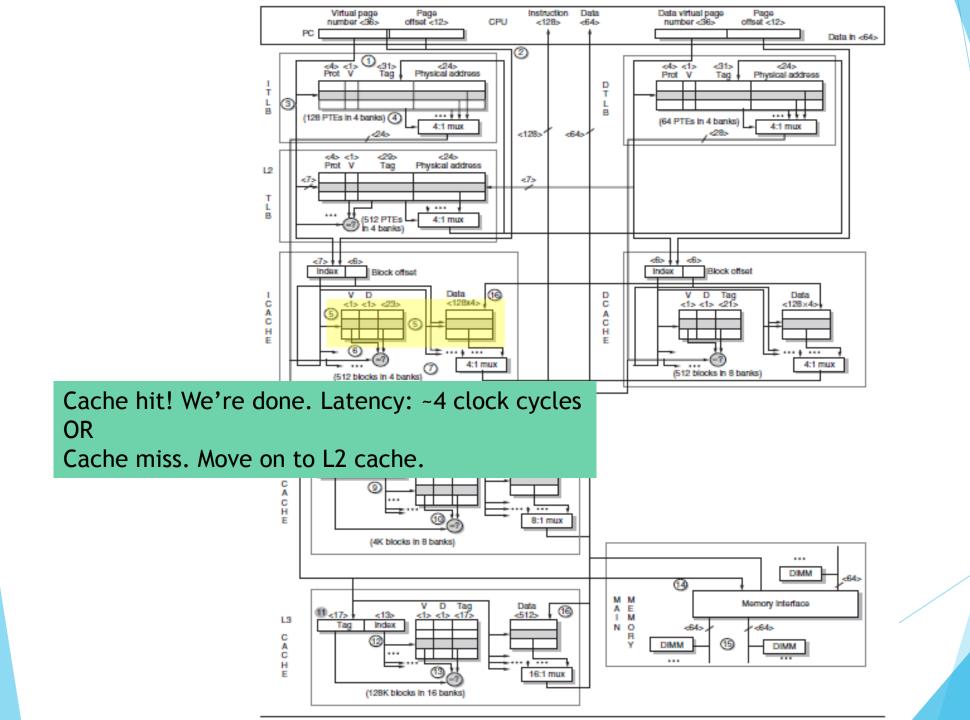

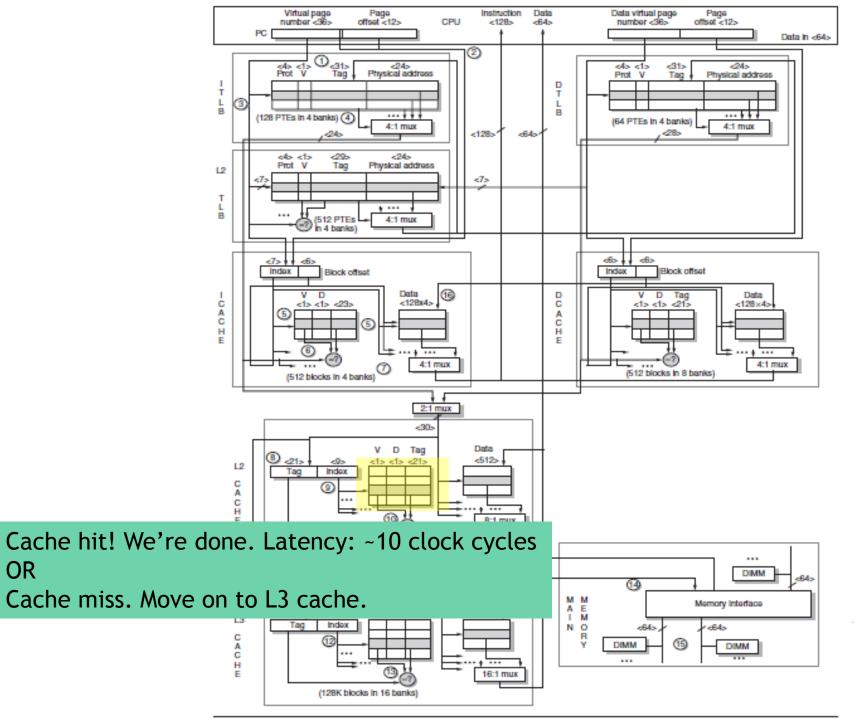

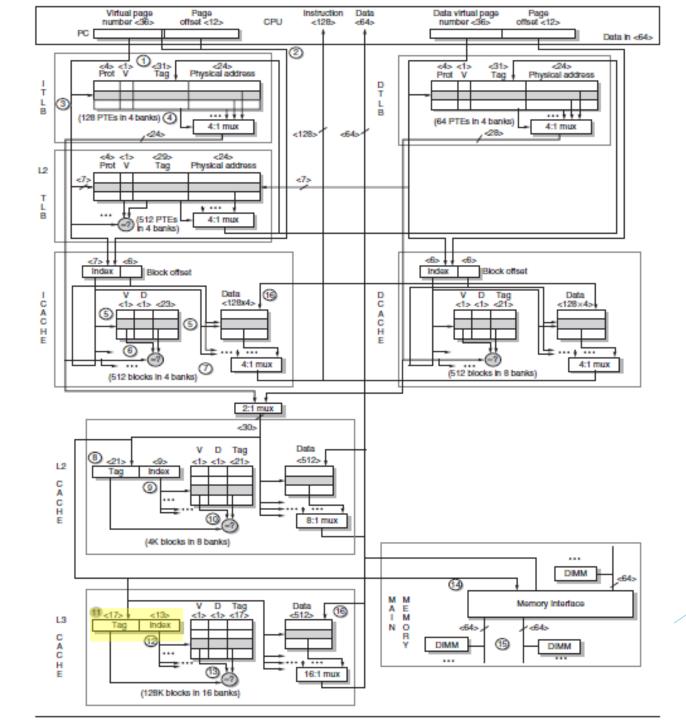

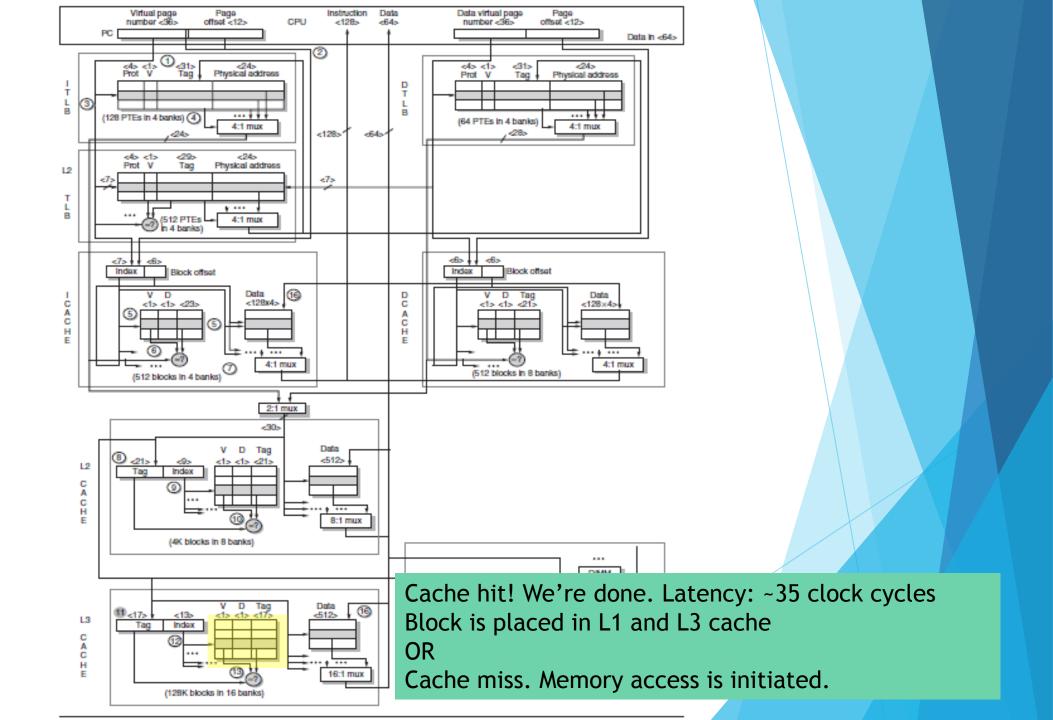

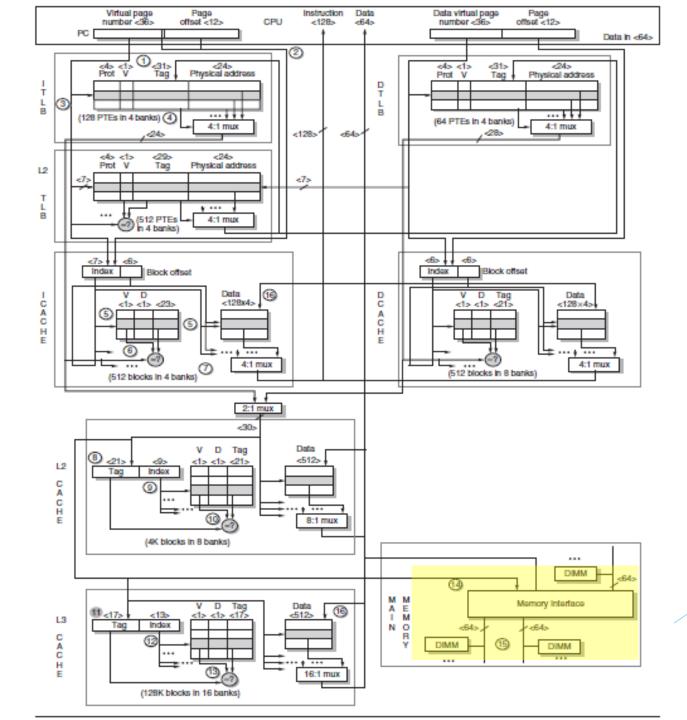

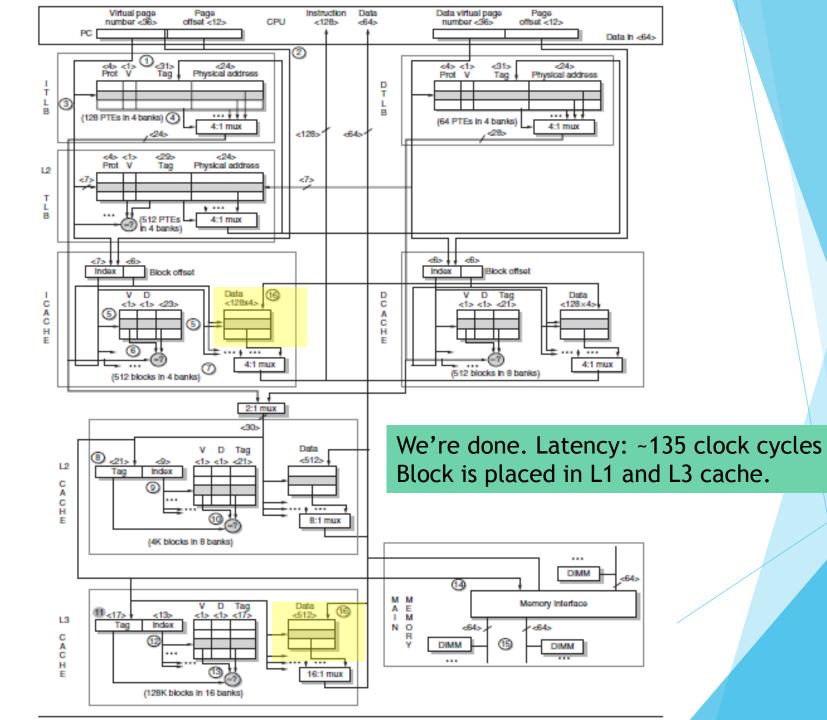

### Figure 9.21 The Core i7 memory system.

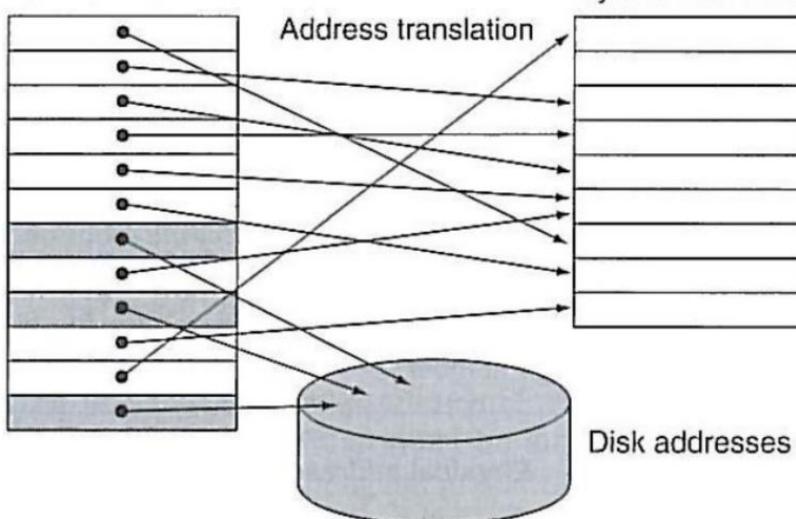

## Virtual Addressing

Virtual addresses

Physical addresses

## **Physical Addressing**

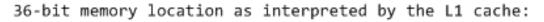

### 2. Search for matching tag in the set

# N-way set associativity (Review)

- Multiple entries per index

- Narrows search area needed to find unused slot

- ▶ i7 4790

- ▶ L1 4x32 KB 8-way

- ▶ L2 4/256 KB 8-way

- L3 shared 8 MB 16-way

# Intel's core i7 TLB design

- Memory cache that stores recent translations of virtual memory to physical addresses for faster retrieval.

- Uses a 2 level cache system

- L1 TLB

- Divided into 2 parts

- Data TLB: 64 4KB entries

- Instruction TLB: 128 4KB entries

- L2 TLB (Services misses in L1 DTLB)

- Can hold translations for 4KB and 2 MB pages (vs. only 4KB)

- 1024 entries (vs. 512)

- 8-way associative (vs. 4-way)

## **TLB Comparisons between generations**

## Nehalem

| Cache |       | Page Size |                  |  |

|-------|-------|-----------|------------------|--|

| Name  | Level | 4 KB      | 2 MB             |  |

| DTLB  | 1st   | 64        | 32               |  |

| ITLB  | 1st   | 128       | 7 / logical core |  |

| STLB  | 2nd   | 512       | none             |  |

| Sandy | Bridge | and  | lvy | Bridge  |

|-------|--------|------|-----|---------|

|       |        |      |     |         |

| Casha | Dama   | Cine | i   | Haswell |

| Cache |       | Page Size |                  |      |  |

|-------|-------|-----------|------------------|------|--|

| Name  | Level | 4 KB      | 2 MB             | 1 GB |  |

| DTLB  | 1st   | 64        | 32               | 4    |  |

| ITLB  | 1st   | 128       | 8 / logical core | none |  |

| STLB  | 2nd   | 512       | none             | none |  |

| Cad  | che   | Page Size |                  |      |

|------|-------|-----------|------------------|------|

| Name | Level | 4 KB      | 2 MB             | 1 GB |

| DTLB | 1st   | 64        | 32               | 4    |

| ITLB | 1st   | 128       | 8 / logical core | none |

| STLB | 2nd   |           | 1024             | none |

# Pseudo-LRU (Intel's core i7 caching algorithm)

- One bit per cache line

- Resets after all lines' bit is set

- Lowest line index with a '0' replaced

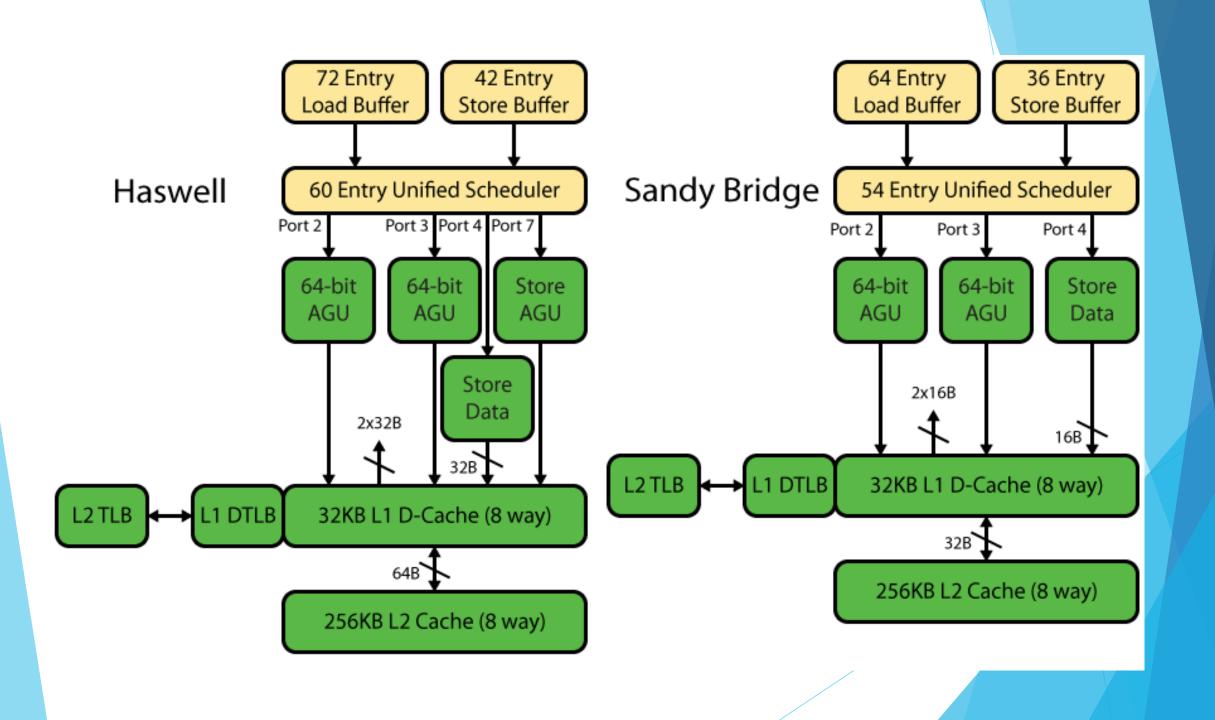

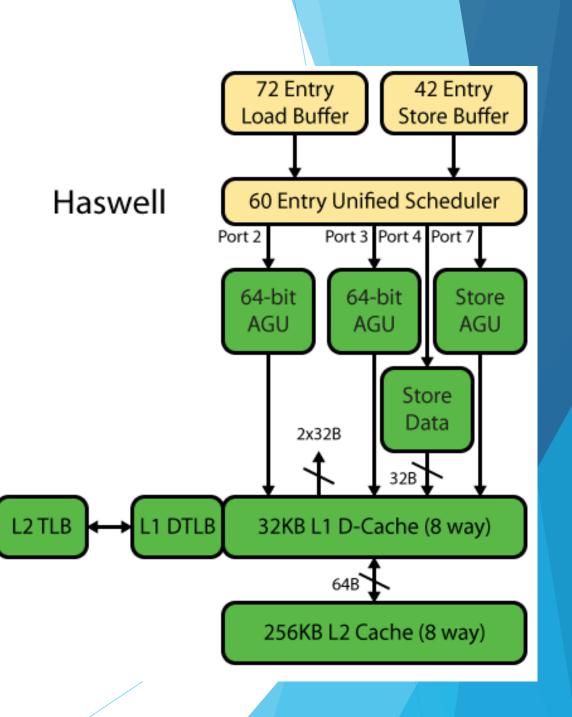

- Port 2 and 3 are the Address Generation Units

- Port 4 for writing data from the core to the L1 Cache

- Additional port added to Haswell

- Haswell can sustain 2 loads and 1 store per cycle "under nearly any circumstances"

- Forwarding latency for AVX loads decreased from 2 to 1 cycle

- AVX: Set of instructions for doing SIMD operations on Intel CPUs

- 4 Split line buffers to resolve unaligned loads (vs 2 in Sandy-bridge)

- Decrease impact of unaligned access

AN X64 PROCESSOR IS SCREAMING ALONG AT BILLIONS OF CYCLES PER SECOND TO RUN THE XNU KERNEL, WHICH IS FRANTICALLY WORKING THROUGH ALL THE POSIX-SPECIFIED ABSTRACTION TO CREATE THE DARWIN SYSTEM UNDERLYING OS X, WHICH IN TURN IS STRAINING ITSELF TO RUN FIREFOX AND ITS GECKO RENDERER, WHICH CREATES A RASH OBJECT WHICH RENDERS DOZENS OF VIDEO FRAMES EVERY SECOND

> BECAUSE I WANTED TO SEE A CAT JUMP INTO A BOX AND FALL OVER.

I AM A GOD.

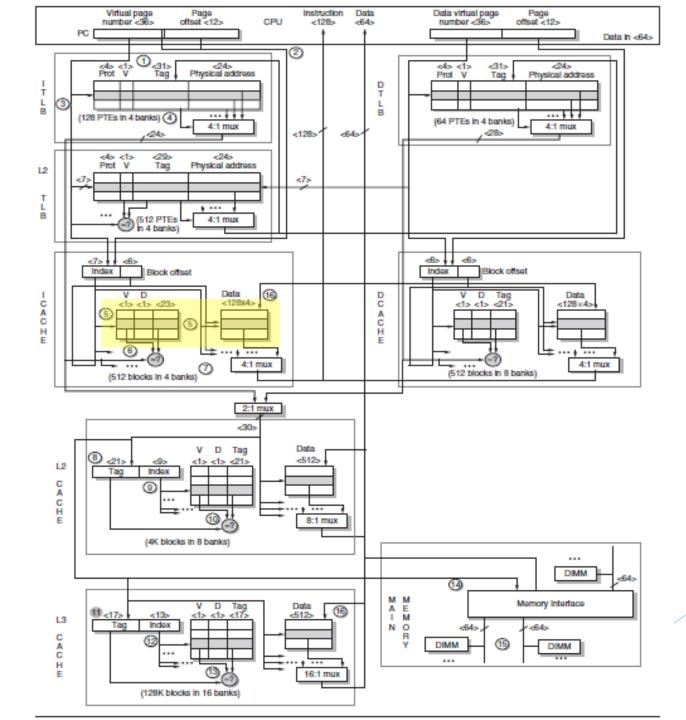

## Haswell L1 Cache

- 32 kb

- 8 way associative

- Writeback

- TLB access & cache tag can occur in parallel

- Does not suffer from bank conflicts (unlike Sandy Bridge)

- Minimum latency: 4 cycles (same as Sandy-Bridge)

- Minimum lock latency of haswell is 12 cycles (sandy-bridge was 16)

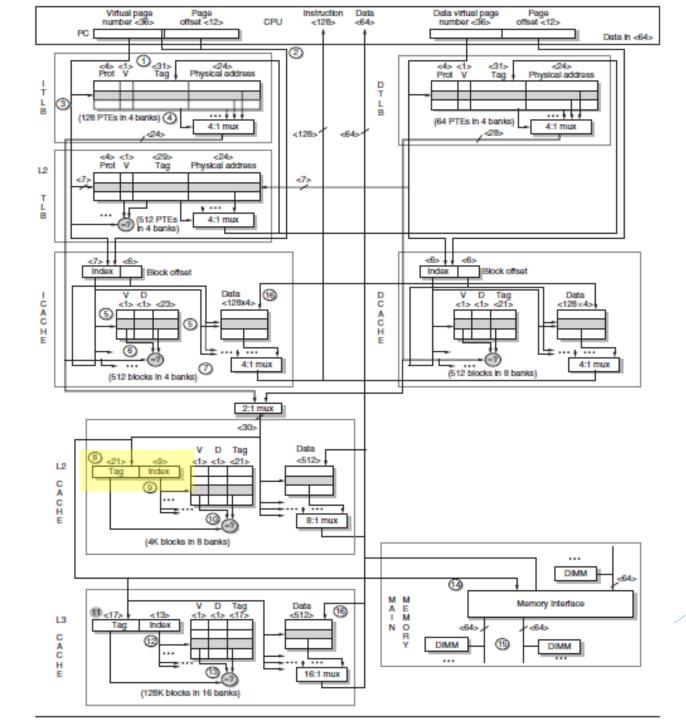

## Haswell L2 Cache

Bandwidth doubled

Can deliver 64 bit line to data or instruction cache every cycle

- 11 cycle latency

- 256 KB for each cache

## Haswell L3 Cache

- Shared between all cores

- Size varies between models and generations between 6MB and 15MB

- Most Haswell models have an 8MB cache

- Size reduced for power efficiency

## **Shared Data**

- Transactional Synchronization Extensions

- Transactional memory

- Hardware Lock Elision

- Backwards Compatible, Windows only

- Uses instruction prefixes to lock and release

- Restricted Transactional Memory

- Newer, more flexible

- Fallback code in case of failure

# **Pre-fetching**

- Fetch Instructions/Data before needed

- On a miss 2 blocks are fetched

- If successful, miss will grab from buffer, and pre-fetch next block

Memory Hierarchy Access Steps

OR

# Generation 5 (Broadwell)

- Currently mobile only (Lower power systems)

- Two cores

- Shrunk to 14 nm

- Power Consumption down to 15 w

- No low-end desktop processors

- Extended instruction set

## Which Processor Should a Buyer Choose?

## **Future Releases**

## Broadwell Desktop

- Many manufacturers plan to skip

- Possibly due to lack of low-end offerings

## Skylake

Second half of 2015

## Desktop Platform – Consumer Roadmap

| Metric               | Nehalem                                            | Sandy Bridge                                      | Haswell                                           |

|----------------------|----------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| L1 Instruction Cache | 32K, 4-way                                         | 32K, 8-way                                        | 32K, 8-way                                        |

| L1 Data Cache        | 32K, 8-way                                         | 32K, 8-way                                        | 32K, 8-way                                        |

| Fastest Load-to-use  | 4 cycles                                           | 4 cycles                                          | 4 cycles                                          |

| Load bandwidth       | 16 Bytes/cycle                                     | 32 Bytes/cycle<br>(banked)                        | 64 Bytes/cycle                                    |

| Store bandwidth      | 16 Bytes/cycle                                     | 16 Bytes/cycle                                    | <b>32 Bytes/cycle</b>                             |

| L2 Unified Cache     | 256K, 8-way                                        | 256K, 8-way                                       | 256K, 8-way                                       |

| Fastest load-to-use  | 10 cycles                                          | 11 cycles                                         | 11 cycles                                         |

| Bandwidth to L1      | 32 Bytes/cycle                                     | 32 Bytes/cycle                                    | 64 Bytes/cycle                                    |

| L1 Instruction TLB   | 4K: 128, 4-way<br>2M/4M: 7/thread                  | 4K: 128, 4-way<br>2M/4M: 8/thread                 | 4K: 128, 4-way<br>2M/4M: 8/thread                 |

| L1 Data TLB          | 4K: 64, 4-way<br>2M/4M: 32, 4-way<br>1G: fractured | 4K: 64, 4-way<br>2M/4M: 32, 4-way<br>1G: 4, 4-way | 4K: 64, 4-way<br>2M/4M: 32, 4-way<br>1G: 4, 4-way |

| L2 Unified TLB       | 4K: 512, 4-way                                     | 4K: 512, 4-way                                    | 4K+2M shared:<br>1024, 8-way                      |

All caches use 64-byte lines

## Conclusion

- Why is it faster?

- Increased Bandwidth

- Doubled the associativity in L2 TLB

- Tri Gate Transistors

- Smaller chip size

- Lower power requirements

- Decreased L3 Cache Size

# Questions?