## NAME:

## USERNAME:

## **CS 2011 Exam 1** D-Term 2008

- Question 1: (10)

- Question 2: (20)

- Question 3: (15)

- Question 4: (20)

- Question 5: (20)

- Question 6: (15)

- TOTAL: \_\_\_\_\_ (100)

Fill in your name and username. DO NOT OPEN THIS TEST UNTIL YOU ARE TOLD TO DO SO.

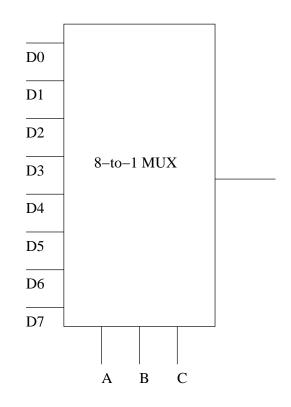

1. (10 points) In class, we saw how a function such as the majority function could be implemented by hard-wiring a multiplexer. Hard-wire the multiplexer pictured below so that it computes the following Boolean function:  $P(A, B, C) = \overline{AB} + C$

- 2. (20 points) An 8-bit byte contains the hexadecimal value xF2. What decimal number does the byte represent if the value in the byte is

- (a) an unsigned integer?

- (b) a signed, two's-complement integer?

3. (15 points) Here's a 32-bit quantity expressed in hexadecimal: x41F20000. The number is in IEEE single-precision floating point. What decimal value does it represent? (Show all work for partial credit.)

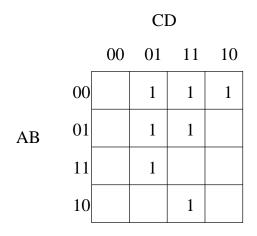

4. Given the following Karnaugh map:

(a) (5 points) Write the sum-of-products equation from which this Karnaugh map is derived. (Don't provide a minimal function yet, just give the function that would lead to the Karnaugh map pictured above.)

- (b) (5 points) Put rectangles around the 1's in the given Karnaugh map to make a minimal mapping.

- (c) (5 points) Use your rectangles to write a minimal sum-of-products equation for the function P.

(d) (5 points) Draw the minimal circuit that corresponds to your equation from part (c).

- 5. (20 points)

- (a) Write machine code instructions (machine code, not assembly language!) that will implement the following pseudo-code:

DO R2 = R2 + R1 R3 = R3 - 1 WHILE R3 != 0

- (b) An LDR instruction, located at location x3100, uses R6 as its base register. The value currently in R6 is x5000.

- i. What is the largest address that the LDR instruction can load from?

- ii. Suppose the offset in an LDR instruction is zero-extended, rather than signextended. Then what would be the largest address the LDR instruction could load from?

6. (15 points) At some instant in time, the state of the LC-3 is partially described by these register values and memory location contents (all given in hex):

| PC:  | x3100 | Memory  |          |  |  |  |  |  |  |

|------|-------|---------|----------|--|--|--|--|--|--|

| IR:  | x0000 | address | contents |  |  |  |  |  |  |

|      |       |         |          |  |  |  |  |  |  |

|      |       | x30FE:  | x3103    |  |  |  |  |  |  |

| RO:  | x0000 | x30FF:  | x3104    |  |  |  |  |  |  |

| R1:  | x1111 | x3100:  | xB9FE    |  |  |  |  |  |  |

| R2:  | x2222 | x3101:  | xCOCO    |  |  |  |  |  |  |

| R3:  | x3333 | x3102:  | xF025    |  |  |  |  |  |  |

| R4:  | x4444 | x3103:  | xABCD    |  |  |  |  |  |  |

| R5:  | x5555 | x3104:  | x30FE    |  |  |  |  |  |  |

| R6:  | x6666 | x3105:  | x2345    |  |  |  |  |  |  |

| R7:  | x7777 |         |          |  |  |  |  |  |  |

|      |       |         |          |  |  |  |  |  |  |

| MAR: | x4000 |         |          |  |  |  |  |  |  |

| MDR: | x5000 |         |          |  |  |  |  |  |  |

Assume the machine in this state is just about to fetch an instruction.

Give the series of micro-operations that show how the data above is transferred throughout the machine as a **single instruction** is fetched, decoded, and executed. Provide a comment for each step. For example, the first step is:

$MAR \leftarrow x3100$  ;; MAR gets the current PC value

|                  |   |    |    | 12 |   |     |    | 8 | 7    | 6 | 5     |      |      | 2   | 1   | 0 |

|------------------|---|----|----|----|---|-----|----|---|------|---|-------|------|------|-----|-----|---|

| ADD+             | 1 |    | 01 |    | I | DR  |    |   | SR1  |   | 0     |      | 0    |     | SR2 | 2 |

| ADD <sup>+</sup> |   | 00 | 01 |    |   | DR  |    | 1 | SR1  |   | 1     | 1    | ii   | nmŧ |     |   |

| AND <sup>+</sup> |   | 01 | 01 |    |   | DR  |    |   | SR1  |   | 0     | 0    | 0    |     | SR2 |   |

| AND <sup>+</sup> |   | 01 | 01 |    |   | DR  |    |   | SR1  |   | 1     |      | ii   | nm! | 5   |   |

| BR               |   | 00 | 00 |    | n | z   | р  |   |      |   | PC    | offs | et9  |     |     |   |

| JMP              |   | 11 | 00 |    | 1 | 000 |    |   | lase |   | I     |      |      | 000 |     |   |

| JSR              |   | 01 | 00 |    | 1 |     |    | 1 |      |   | offse | et11 |      |     |     |   |

| JSRR             |   | 01 | 00 |    | 0 | 0   | 0  | B | lase |   | I     |      |      | 000 |     |   |

| LD <sup>+</sup>  | 1 | 00 | 10 |    |   | DR  |    |   |      |   | PC    | offs | et9  |     |     |   |

| LDI+             |   | 10 | 10 |    |   | DR  |    |   |      |   | PC    | offs | et9  |     |     |   |

| LDR+             |   | 01 |    |    | 1 | DR  |    |   | lase |   |       | I    | offe | et6 |     |   |

| LEA <sup>+</sup> | 1 | 11 | 10 |    | 1 | DR  |    |   |      |   | I     | offs |      |     |     |   |

| NOT+             |   | 10 | 01 |    |   | DR  |    |   | SR   |   |       |      |      | 111 |     |   |

| RET              | 1 | 11 | 00 |    | 1 | 000 |    | 1 | 111  |   |       |      |      | 000 |     |   |

| RTI              |   | 10 | 00 |    |   |     |    |   |      |   |       |      |      |     |     |   |

| ST               |   | 00 | 11 |    |   | SR  |    |   |      |   | PC    | offs | et9  |     |     |   |

| STI              | 1 | 10 | 11 |    |   | SR  |    |   |      | I | PC    | offs | et9  |     |     |   |

| STR              |   | 01 | 1  |    |   | SR  |    |   | lase |   |       |      | offs | et6 |     |   |

| TRAP             |   | 11 |    |    |   | 00  | 00 |   |      | I | t     | rapv |      |     |     |   |

| reserved         |   | 11 | 01 |    |   |     |    |   |      | I |       | I    | _    |     |     |   |

| L                |   |    |    |    |   |     |    |   |      |   |       |      |      |     |     |   |